www.ti.com.cn ZHCS611 – DECEMBER 2011

# 具有双倍速率低压差分信号(DDR LVDS)和 CMOS 输出的14 位,65每秒百万次采样(MSPS)模数转换器(ADC)

查询样品: ADS6142-HT

## 特性

- 最大采样率

- 无丢码的14位分辨率

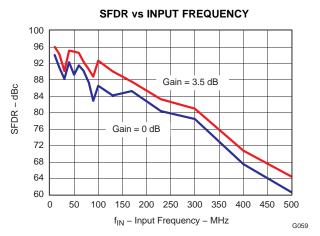

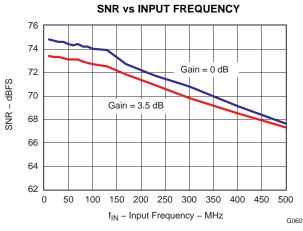

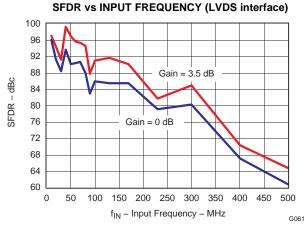

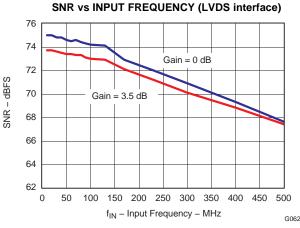

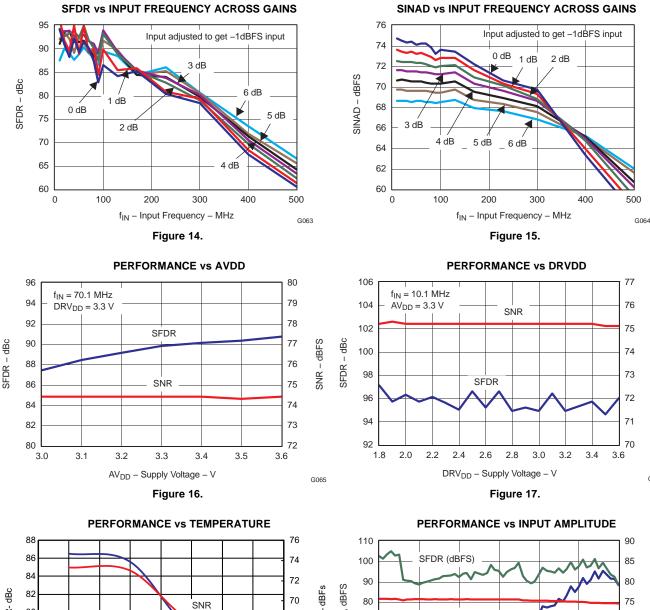

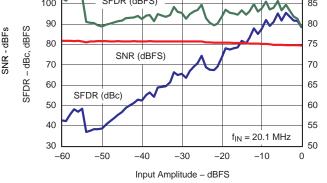

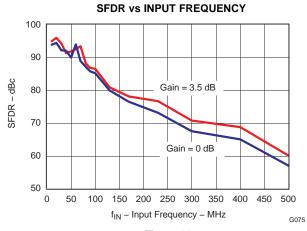

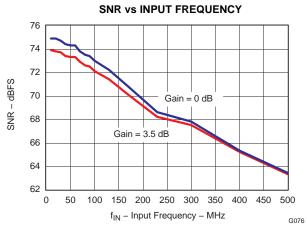

- 用于信噪比(SNR)/无杂散动态范围(SFDR)权衡的3.5dB粗调增益和最高6dB可编程微调增益

- 并行CMOS和双倍速率(DDR) LVDS输出选项

- 支持正弦,低压COMS(LVCOMS),低电压正射极 耦合逻辑(LVPECL),LVDS时钟输入,和时钟振幅 低至400mV<sub>PP</sub>

- 时钟占空比稳定器

- 支持外部基准的内部基准

- 无需为基准提供外部退偶装置

- 可编程输出时钟位置和数据捕捉的驱动强度

- 3.3V模拟和1数字电源

#### 应用范围

- 潜孔钻孔

- 高温环境

- 无线通信基础设施

- 软件定义无线电

- 功率放大器线性化

#### 802.16d/e

- 测试和测量仪器

- 高清音频

- 医疗成像

- 雷达系统

支持极端温度环境下的应用

- 受控基线

- 一个组装/测试场所

- 一个制造场所

- 可在极端温度范围内(-40°C/210°C)工作(1)

- 延长的产品使用寿命周期

- 延长产品的变更通知周期

- 产品可追溯性

- 德州仪器高温产品利用高度优化的硅(芯片)解决方案,此解决方案对设计和制造工艺进行了提升以在拓展的温度范围内大大地提高性能。所有器件可在最大额定温度下连续运行1000小时。

**ADS6142-HT**

(1) 可定制温度范围

#### 说明

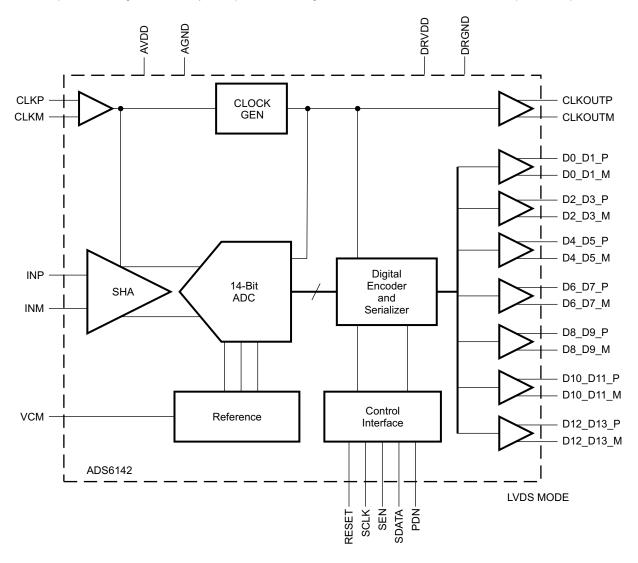

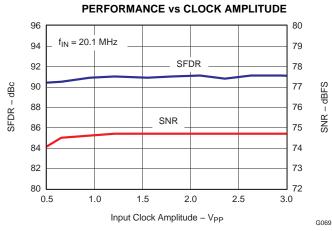

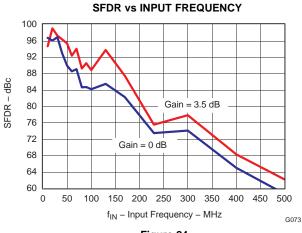

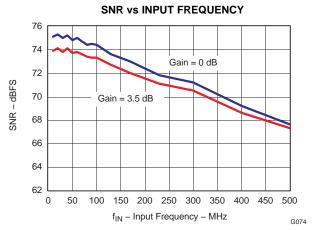

ADS6142是一款高性能和低功率耗散14位模拟/数字(A/D)转换器,此转换器采样频率为65每秒百万次采样(MSPS)。 即使在高输入频率下,一个内部高带宽采样和保持以及一个低抖动时钟缓冲器可帮助实现高信噪比(SNR)和宽无杂散动态范围(SFDR)。

ADS6142特有粗调和微调增益选项,在较低全幅模拟输入范围内,可改进SFDR性能。

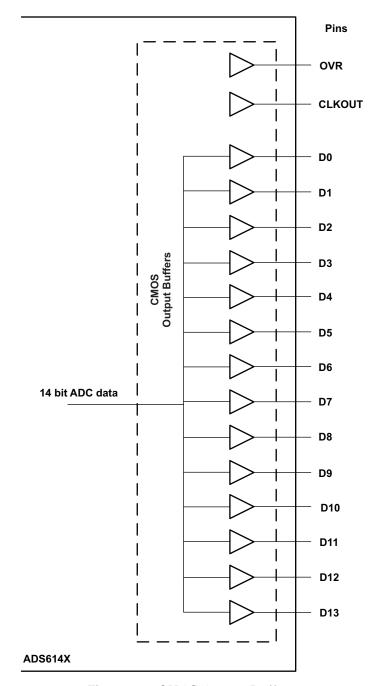

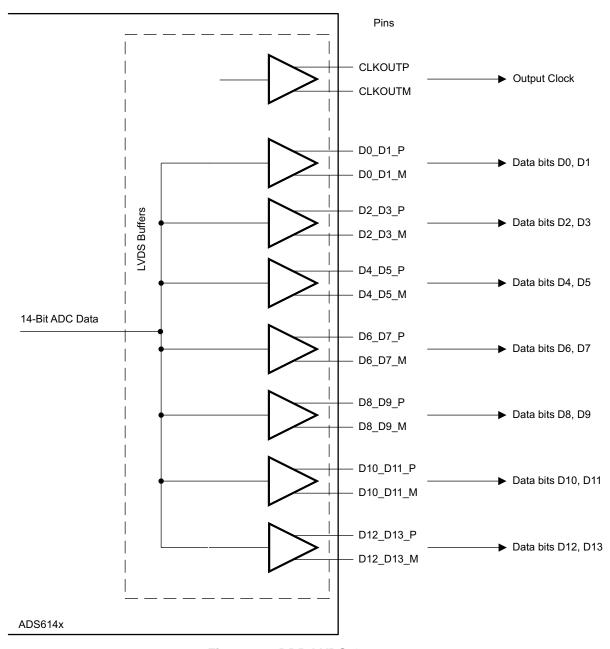

此数字输出是并行CMOS或者是DDR(双倍速率)LVDS。 有几个特性可以使数据捕捉更加容易 - 输出时钟位置的控制和输出缓冲器驱动能力,LVDS电流,和内部终止可编程性。

输出接口类型,增益,和其它功能可使用**3**线制串口进行编程。或者,可使用专用并行引脚对一些功能进行配置,因此此器件驱动到所需状态。

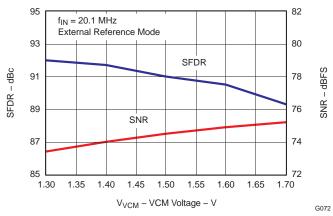

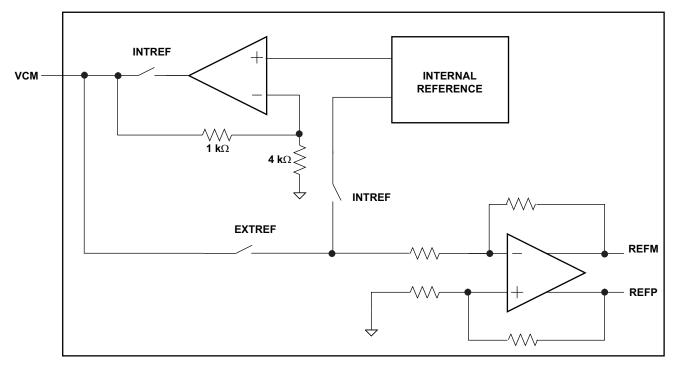

ADS6142在包含内部基准的同时去除了传统的基准引脚和相关的外部退偶装置。 也支持外部基准模式。

ADS6142可在极端温度范围(-40°C至 210°C)内工作。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

ZHCS611 – DECEMBER 2011 www.ti.com.cn

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

Table 1. ORDERING INFORMATION(1)

| TA             | PACKAGE <sup>(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|------------------------|-----------------------|------------------|

| –40°C to 210°C | KGD (bare die)         | ADS6142SKGD1          | NA               |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

<sup>(2)</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

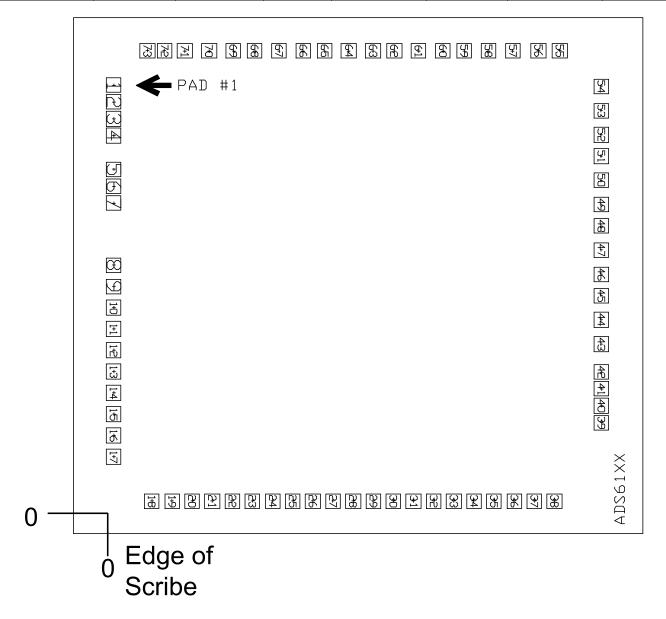

#### **BARE DIE INFORMATION**

| DIE<br>SIZE                           | DIE PAD<br>SIZE | DIE PAD<br>COORDINATES | DIE<br>THICKNESS | BACKSIDE FINISH        | BACKSIDE<br>POTENTIAL | BOND PAD<br>METALLIZATION<br>COMPOSITION | BOND PAD<br>THICKNESS |

|---------------------------------------|-----------------|------------------------|------------------|------------------------|-----------------------|------------------------------------------|-----------------------|

| 2715 x 2460 µm<br>96.85 x 106.89 mils | 70 x 70 μm      | See Table 2            | 11 mils          | Silicon with backgrind | DRVSS                 | Ti/Al-Cu/TiN                             | 1100 nm               |

## **Table 2. BOND PAD COORDINATES**

| DESCRIPTION | PAD NUMBER | X MIN    | Y MIN          | X MAX    | Y MAX   |

|-------------|------------|----------|----------------|----------|---------|

| DRVDD       | 1          | 80.92    | 2065           | 150.92   | 2135    |

| N/C         | 2          | 80.92    | 1984.5         | 150.92   | 2054.5  |

| N/C         | 3          | 80.92    | 1904           | 150.92   | 1974    |

| RESET       | 4          | 80.92    | 1823.5         | 150.92   | 1893.5  |

| SCLK        | 5          | 80.92    | 1662.5         | 150.92   | 1732.5  |

| SDATA       | 6          | 80.92    | 1582           | 150.92   | 1652    |

| SEN         | 7          | 80.92    | 1501.5         | 150.92   | 1571.5  |

| N/C         | 8          | 80.92    | 1206.1         | 150.92   | 1276.1  |

| N/C         | 9          | 80.92    | 1104.6         | 150.92   | 1174.6  |

| AGND        | 10         | 80.92    | 1003.1         | 150.92   | 1073.1  |

| AGND        | 11         | 80.92    | 901.6          | 150.92   | 971.6   |

| AGND        | 12         | 80.92    | 800.1          | 150.92   | 870.1   |

| CLKP        | 13         | 80.92    | 698.6          | 150.92   | 768.6   |

| CLKP        | 14         | 80.92    | 597.1          | 150.92   | 667.1   |

| CLKM        | 15         | 80.92    | 495.6          | 150.92   | 565.6   |

| CLKM        | 16         | 80.92    | 394.1          | 150.92   | 464.1   |

| N/C         | 17         | 80.92    | 292.6          | 150.92   | 362.6   |

| N/C         | 18         | 262.5    | 80.92          | 332.5    | 150.92  |

| AGND        | 19         | 358.365  | 80.92          | 428.365  | 150.92  |

| AGND        | 20         | 454.23   | 80.92          | 524.23   | 150.92  |

| N/C         | 21         | 550.095  | 80.92          | 620.095  | 150.92  |

|             |            |          |                |          |         |

| INP<br>INP  | 22         | 645.96   | 80.92          | 715.96   | 150.92  |

| INM         | 24         | 741.825  | 80.92<br>80.92 | 811.825  | 150.92  |

| INM         | 25         | 837.69   |                | 907.69   | 150.92  |

|             |            | 933.555  | 80.92          | 1003.555 | 150.92  |

| N/C         | 26         | 1029.42  | 80.92          | 1099.42  | 150.92  |

| AGND        | 27         | 1125.285 | 80.92          | 1195.285 | 150.92  |

| AGND        | 28         | 1221.15  | 80.92          | 1291.15  | 150.92  |

| N/C         | 29         | 1317.015 | 80.92          | 1387.015 | 150.92  |

| AVDD        | 30         | 1412.88  | 80.92          | 1482.88  | 150.92  |

| AVDD        | 31         | 1508.745 | 80.92          | 1578.745 | 150.92  |

| VCM         | 32         | 1604.61  | 80.92          | 1674.61  | 150.92  |

| VCM         | 33         | 1700.475 | 80.92          | 1770.475 | 150.92  |

| N/C         | 34         | 1796.34  | 80.92          | 1866.34  | 150.92  |

| N/C         | 35         | 1892.205 | 80.92          | 1962.205 | 150.92  |

| N/C         | 36         | 1988.07  | 80.92          | 2058.07  | 150.92  |

| AVDD        | 37         | 2083.935 | 80.92          | 2153.935 | 150.92  |

| PDN         | 38         | 2179.8   | 80.92          | 2249.8   | 150.92  |

| N/C         | 39         | 2404.08  | 455            | 2474.08  | 525     |

| N/C         | 40         | 2404.08  | 535.5          | 2474.08  | 605.5   |

| N/C         | 41         | 2404.08  | 616            | 2474.08  | 686     |

| N/C         | 42         | 2404.08  | 696.5          | 2474.08  | 766.5   |

| D0          | 43         | 2402.925 | 829.71         | 2472.925 | 899.71  |

| N/C         | 44         | 2402.925 | 945.28         | 2472.925 | 1015.28 |

| D1          | 45         | 2402.925 | 1060.85        | 2472.925 | 1130.85 |

| D2          | 46         | 2402.925 | 1162.21        | 2472.925 | 1232.21 |

| SUBST       | 47         | 2402.925 | 1277.78        | 2472.925 | 1347.78 |

## Table 2. BOND PAD COORDINATES (continued)

| DESCRIPTION                            | PAD NUMBER | X MIN    | Y MIN    | X MAX    | Y MAX    |

|----------------------------------------|------------|----------|----------|----------|----------|

| D3                                     | 48         | 2402.925 | 1393.35  | 2472.925 | 1463.35  |

| D4                                     | 49         | 2402.925 | 1494.71  | 2472.925 | 1564.71  |

| SUBST                                  | 50         | 2402.925 | 1610.28  | 2472.925 | 1680.28  |

| D5                                     | 51         | 2402.925 | 1725.85  | 2472.925 | 1795.85  |

| D6                                     | 52         | 2402.925 | 1827.21  | 2472.925 | 1897.21  |

| N/C                                    | 53         | 2402.925 | 1942.78  | 2472.925 | 2012.78  |

| D7                                     | 54         | 2402.925 | 2058.35  | 2472.925 | 2128.35  |

| SUBST                                  | 55         | 2205     | 2229.08  | 2275     | 2299.08  |

| SUBST                                  | 56         | 2103.5   | 2229.08  | 2173.5   | 2299.08  |

| OVR                                    | 57         | 1980.79  | 2227.925 | 2050.79  | 2297.925 |

| SUBST                                  | 58         | 1865.22  | 2227.925 | 1935.22  | 2297.925 |

| CLKOUT                                 | 59         | 1749.65  | 2227.925 | 1819.65  | 2297.925 |

| N/C                                    | 60         | 1648.29  | 2227.925 | 1718.29  | 2297.925 |

| SUBST                                  | 61         | 1532.72  | 2227.925 | 1602.72  | 2297.925 |

| N/C                                    | 62         | 1417.15  | 2227.925 | 1487.15  | 2297.925 |

| D8                                     | 63         | 1315.79  | 2227.925 | 1385.79  | 2297.925 |

| SUBST                                  | 64         | 1200.22  | 2227.925 | 1270.22  | 2297.925 |

| D9                                     | 65         | 1084.65  | 2227.925 | 1154.65  | 2297.925 |

| D10                                    | 66         | 983.29   | 2227.925 | 1053.29  | 2297.925 |

| SUBST                                  | 67         | 867.72   | 2227.925 | 937.72   | 2297.925 |

| D11                                    | 68         | 752.15   | 2227.925 | 822.15   | 2297.925 |

| D12                                    | 69         | 650.79   | 2227.925 | 720.79   | 2297.925 |

| SUBST                                  | 70         | 535.22   | 2227.925 | 605.22   | 2297.925 |

| D13                                    | 71         | 419.65   | 2227.925 | 489.65   | 2297.925 |

| SUBST                                  | 72         | 322      | 2229.08  | 392      | 2299.08  |

| DRVDD                                  | 73         | 241.5    | 2229.08  | 311.5    | 2299.08  |

| Substrate should be connected to DRVSS |            |          |          |          |          |

## TEXAS INSTRUMENTS

## ABSOLUTE MAXIMUM RATINGS(1)

|                  |                                                         | VALUE                              | UNIT |

|------------------|---------------------------------------------------------|------------------------------------|------|

| V                | Supply voltage range, AVDD                              | -0.3 to 3.9                        | V    |

| VI               | Supply voltage range, DRVDD                             | -0.3 to 3.9                        | V    |

|                  | Voltage between AGND and DRGND                          | -0.3 to 0.3                        | V    |

|                  | Voltage between AVDD to DRVDD                           | -0.3 to 3.3                        | V    |

|                  | Voltage applied to VCM pin (in external reference mode) | -0.3 to 2                          | V    |

|                  | Voltage applied to analog input pins, INP and INM       | -0.3 to minimum ( 3.6, AVDD + 0.3) | V    |

|                  | Voltage applied to analog input pins, CLKP and CLKM     | -0.3 to (AVDD + 0.3)               | V    |

| TJ               | Operating junction temperature range                    | -40 to 210                         | °C   |

| T <sub>stg</sub> | Storage temperature range                               | -65 to 210                         | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                                                                 |                                                   |                                                | Tj = - | -40°C to 125°    | С    |                     | Tj = 210°C       |      |          |

|-----------------------------------------------------------------|---------------------------------------------------|------------------------------------------------|--------|------------------|------|---------------------|------------------|------|----------|

|                                                                 |                                                   |                                                | MIN    | NOM              | MAX  | MIN                 | NOM              | MAX  | UNIT     |

| SUPPLI                                                          | ES                                                | •                                              |        |                  |      |                     |                  |      |          |

| AVDD                                                            | Analog supply voltage                             |                                                | 3      | 3.3              | 3.6  | 3                   | 3.3              | 3.6  | V        |

| DRVDD                                                           | Output buffer supply                              | CMOS Interface                                 | 1.65   | 1.8 to 3.3       | 3.6  | 1.65                | 1.8 to 3.3       | 3.6  | V        |

| טעאט                                                            | voltage                                           | LVDS Interface                                 | 3      | 3.3              | 3.6  | 3                   | 3.3              | 3.6  | V        |

| ANALO                                                           | G INPUTS                                          |                                                |        |                  |      |                     |                  |      |          |

|                                                                 | Differential input voltage                        | range                                          |        | 2                |      |                     | 2                |      | $V_{pp}$ |

| V <sub>IC</sub>                                                 | Input common-mode vol                             | Itage                                          |        | 1.5 ± 0.1        |      |                     | 1.5 ± 0.1        |      | V        |

|                                                                 | Voltage applied on VCM in external reference mode |                                                | 1.45   | 1.5              | 1.55 | 1.45                | 1.5              | 1.55 | V        |

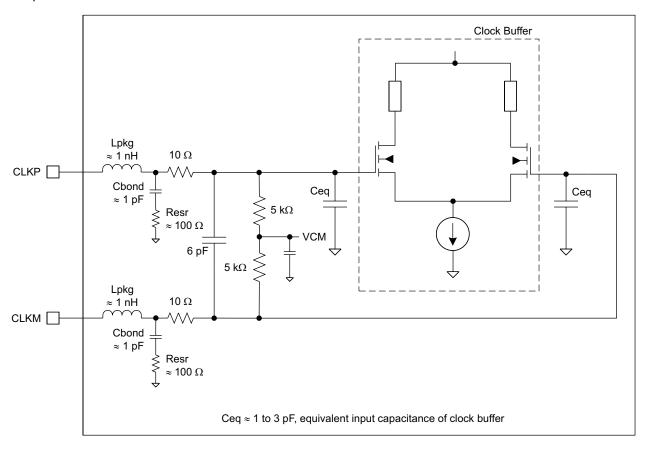

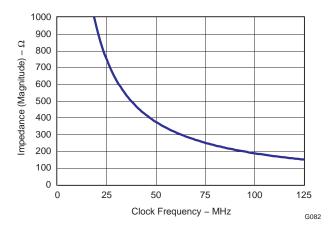

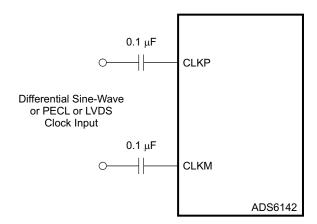

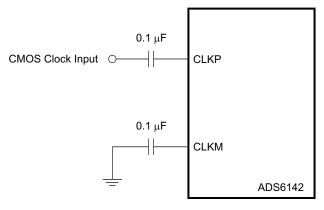

| CLOCK                                                           | INPUT                                             |                                                |        |                  |      |                     |                  |      |          |

|                                                                 | Input clock sample rate,                          | F <sub>S</sub>                                 | 1      |                  | 65   | 1                   |                  | 65   | MSPS     |

|                                                                 |                                                   | Sine wave, ac-coupled                          | 0.4    | 1.5              |      | 0.4                 | 1.5              |      |          |

|                                                                 | Input clock amplitude differential                | LVPECL, ac-coupled                             |        | ± 0.8            |      |                     | ± 0.8            |      | \/       |

|                                                                 | (V <sub>CLKP</sub> – V <sub>CLKM</sub> )          | LVDS, ac-coupled                               |        | ± 0.35           |      |                     | ± 0.35           |      | $V_{pp}$ |

|                                                                 | ( OZIMI)                                          | LVCMOS, ac-coupled                             |        | 3.3              |      |                     | 3.3              |      |          |

|                                                                 | Input Clock duty cycle                            |                                                | 35%    | 50%              | 65%  | 35%                 | 50%              | 65%  |          |

| DIGITAL                                                         | L OUTPUTS                                         |                                                |        |                  | ·    |                     |                  |      |          |

|                                                                 |                                                   | For C <sub>LOAD</sub> ≤ 5 pF and DRVDD ≥ 2.2 V |        | DEFAULT strength |      |                     | DEFAULT strength |      |          |

|                                                                 | Output buffer drive strength (1)                  | For C <sub>LOAD</sub> > 5 pF and DRVDD ≥ 2.2 V |        | MAXIMUM strength |      | MAXIMUM<br>strength |                  |      |          |

|                                                                 |                                                   | For DRVDD < 2.2 V                              |        | MAXIMUM strength |      |                     | MAXIMUM strength |      |          |

|                                                                 |                                                   | CMOS Interface, maximum buffer strength        |        | 10               |      |                     | 10               |      |          |

| Maximum external load capacitance from each output pin to DRGND |                                                   | LVDS Interface, without internal termination   | 5      |                  |      | 5                   |                  |      | pF       |

|                                                                 |                                                   | LVDS Interface, with internal termination      |        | 10               |      |                     | 10               |      |          |

| R <sub>LOAD</sub>                                               | Differential load resistan LVDS output pairs      | ce (external) between the                      |        | 100              |      | 100                 |                  |      | Ω        |

| T <sub>J</sub>                                                  | Operating junction temp                           | erature range                                  | -40    |                  | 125  |                     |                  | 210  | °C       |

<sup>(1)</sup> See Output Buffer Strength Programmability in the application section.

#### **ELECTRICAL CHARACTERISTICS**

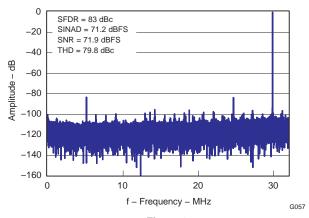

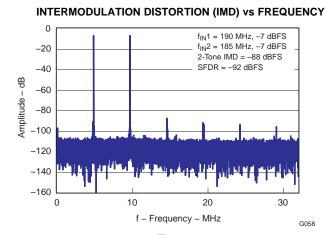

Typical values are at 25°C, AVDD = DRVDD = 3.3 V, maximum rated sampling frequency, 50% clock duty cycle, -1 dBFS differential analog input, internal reference mode, applies to CMOS and LVDS interfaces, unless otherwise noted.

|                                           | PARAMETER                                                                                                      | Tj = -       | 40°C to 125  | °C        | Tj    | = 210°C |     | UNIT     |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------|--------------|-----------|-------|---------|-----|----------|

|                                           | PARAMETER                                                                                                      | MIN          | TYP          | MAX       | MIN   | TYP     | MAX | UNII     |

| RESOLUTIO                                 | ON .                                                                                                           |              | 14           |           |       | 14      |     | Bits     |

| ANALOG IN                                 | PUT                                                                                                            | ,            |              |           |       |         |     |          |

|                                           | Differential input voltage range                                                                               |              | 2            |           |       | 2       |     | $V_{PP}$ |

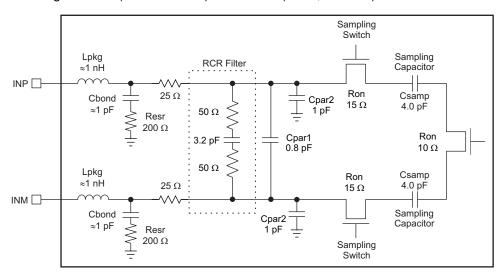

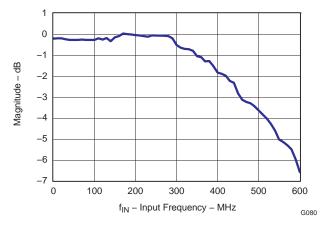

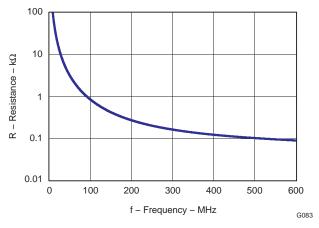

|                                           | Differential input resistance (dc), see Figure 37                                                              |              | > 1          |           |       | > 1     |     | МΩ       |

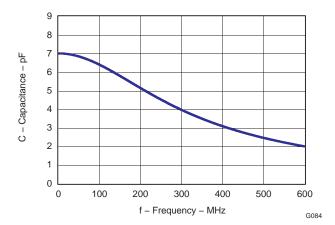

|                                           | Differential input capacitance, see Figure 38                                                                  |              | 7            |           |       | 7       |     | pF       |

|                                           | Analog input bandwidth                                                                                         |              | 450          |           |       | 300     |     | MHz      |

|                                           | Analog input common-mode current (per input pin of each ADC)                                                   |              | 92           |           |       | 95      |     | μΑ       |

| REFERENCI                                 | E VOLTAGES                                                                                                     |              |              |           |       |         |     |          |

| VREFB                                     | Internal reference bottom voltage                                                                              |              | 1            |           |       | 1       |     | V        |

| VREFT                                     | Internal reference top voltage                                                                                 |              | 2            |           |       | 2       |     | V        |

| $\Delta V_{REF}$                          | Internal reference error (VREFT–VREFB)                                                                         | -30          | ±5           | 30        | -55   | ±5      | 55  | mV       |

| V <sub>CM</sub>                           | Common-mode output voltage 1.5 1.5                                                                             |              | 1.5          |           | V     |         |     |          |

| V <sub>CM</sub> Output current capability |                                                                                                                | ·            | 4            |           |       | 4       |     | mA       |

| DC ACCURA                                 | ACY                                                                                                            | ·            |              |           |       |         | '   |          |

|                                           | No missing codes                                                                                               |              | Specified    |           |       | Specifi | ed  |          |

| Eo                                        | Offset error                                                                                                   | -11          | ±2           | 11        | -13   | ±10     | 13  | mV       |

|                                           | Offset error temperature coefficient                                                                           | ·            | 0.04         |           |       | 0.06    |     | mV/°C    |

|                                           | There are two sources of gain error – internal reference in                                                    | naccuracy ar | nd channel g | ain error |       |         | ,   |          |

| E <sub>GREF</sub>                         | Gain error due to internal reference inaccuracy alone, ( $\Delta V_{REF}/2$ ) %                                | -1           | 0.6          | 1         | -1    | 0.65    | 1   | % FS     |

| E <sub>GCHAN</sub>                        | Gain error of channel alone <sup>(1)</sup>                                                                     | ,            | ±0.3         |           |       | ±0.3    |     | % FS     |

|                                           | Channel gain error temperature coefficient                                                                     | ·            | 0.005        |           |       |         |     | Δ%/°C    |

| DNL                                       | Differential nonlinearity                                                                                      | -0.95        | 0.5          | 2         | -0.99 | ±0.5    | 2.5 | LSB      |

| INL                                       | Integral nonlinearity                                                                                          | -10          | ±2           | 10        | -18   | ±6      | 18  | LSB      |

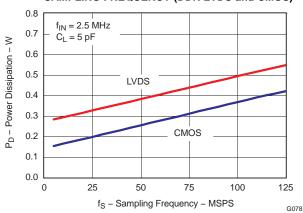

| POWER SU                                  | PPLY                                                                                                           |              |              |           |       |         |     |          |

| I <sub>AVDD</sub>                         | Analog supply current                                                                                          | ·            | 0.75         |           |       | 0.76    |     | mA       |

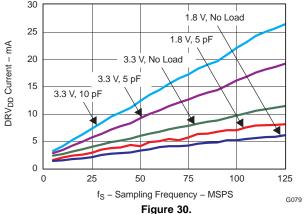

| I <sub>DRVDD</sub>                        | Digital supply current, <b>CMOS</b> interface, DRVDD = 1.8 V, 4 No load capacitance, $F_{in}$ = 2 MHz $^{(2)}$ |              | 4            |           | mA    |         |     |          |

| DRVDD                                     | Digital supply current, <b>LVDS</b> interface,<br>DRVDD = 3.3 V,<br>with 100-Ω external termination            |              | 21           |           |       | 48      |     | mA       |

|                                           | Total power, <b>CMOS</b> , DRVDD = $3.3 \text{ V}^{(3)}$                                                       |              | 418          | 450       |       | 422     | 500 | mW       |

|                                           | Global power down                                                                                              |              | 30           | 60        |       | 30      | 70  | mW       |

<sup>(1)</sup> Specified by design and characterization; not tested in production.

In CMOS mode, the DRVDD current scales with the sampling frequency and the load capacitance on the output pins (see Figure 30). The maximum DRVDD current depends on the actual load capacitance on the digital output lines. Note that the maximum recommended load capacitance is 10 pF.

## **ELECTRICAL CHARACTERISTICS**

Typical values are at 25°C, AVDD = DRVDD = 3.3 V, maximum rated sampling frequency, 50% clock duty cycle, -1 dBFS differential analog input, internal reference mode, applies to CMOS and LVDS interfaces, unless otherwise noted.

| PARAMETER                                                | TES                           | T CONDITIONS       | Tj = -4 | 0°C to 125° | C   | Tj   | j= 210°C |     | UNIT     |

|----------------------------------------------------------|-------------------------------|--------------------|---------|-------------|-----|------|----------|-----|----------|

| FANAMETER                                                | 163                           | 1 CONDITIONS       | MIN     | TYP         | MAX | MIN  | TYP      | MAX | JINIT    |

| DYNAMIC AC CHARACT                                       | ERISTICS                      |                    |         |             |     |      |          |     |          |

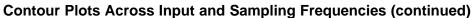

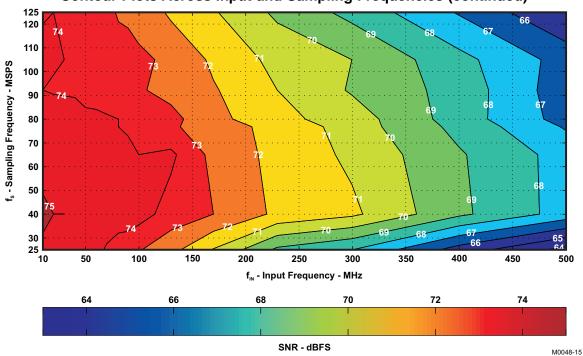

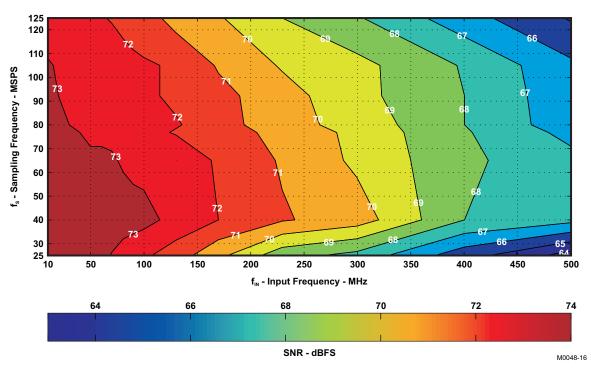

|                                                          | F <sub>in</sub> = 10 MHz      |                    |         | 74.7        |     |      |          |     |          |

|                                                          | F <sub>in</sub> = 50 MHz      |                    |         | 74.4        |     |      |          |     |          |

| SNR                                                      | F <sub>in</sub> = 70 MHz      |                    | 61.5    | 74.4        |     | 57.5 | 74       |     |          |

| Signal-to-noise ratio,                                   | F <sub>in</sub> = 170 MHz     | 0 dB Gain          |         | 72.7        |     |      |          |     | dBFS     |

| CIVIOS                                                   | .                             | 3.5 dB Coarse gain |         | 71.8        |     |      |          |     |          |

|                                                          | F <sub>in</sub> = 230 MHz     | 0 dB Gain          |         | 71.7        |     |      | 65.5     |     |          |

|                                                          |                               | 3.5 dB Coarse gain |         | 70.9        |     |      | 63       |     |          |

|                                                          | F <sub>in</sub> = 10 MHz      |                    |         | 75          |     |      |          |     |          |

|                                                          | F <sub>in</sub> = 50 MHz      |                    |         | 74.6        |     |      |          |     |          |

| SNR<br>Signal-to-noise ratio,<br>LVDS                    | F <sub>in</sub> = 70 MHz      |                    | 68      | 74.6        |     | 62   | 75       |     |          |

|                                                          | F <sub>in</sub> = 170 MHz     | 0 dB Gain          |         | 72.9        |     |      |          |     | dBFS     |

| LANO                                                     | . <sub>III</sub> = 17 0 WI 12 | 3.5 dB Coarse gain |         | 72.1        |     |      |          |     |          |

|                                                          | F <sub>in</sub> = 230 MHz     | 0 dB Gain          |         | 72          |     |      | 60       |     |          |

|                                                          | . IN - 200 IVII IZ            | 3.5 dB Coarse gain |         | 71.2        |     |      |          |     |          |

| RMS output noise                                         | Inputs tied to comm           | non-mode           |         | 1.05        |     |      |          |     | LSB      |

|                                                          | F <sub>in</sub> = 10 MHz      |                    |         | 74.6        |     |      |          |     |          |

| SINAD<br>Signal-to-noise and<br>distortion ratio<br>CMOS | $F_{in} = 50 \text{ MHz}$     |                    | 74.1    |             |     |      |          |     |          |

|                                                          | F <sub>in</sub> = 70 MHz      |                    | 60.5    | 74.0        |     | 56.5 | 74       |     |          |

|                                                          | E 470 MH-                     | 0 dB Gain          |         | 72.2        |     |      |          |     | dBFS     |

|                                                          | F <sub>in</sub> = 170 MHz     | 3.5 dB Coarse gain |         | 71.5        |     |      |          |     |          |

|                                                          | F 000 MH-                     | 0 dB Gain          |         | 70.6        |     |      | 56       |     |          |

|                                                          | $F_{in} = 230 \text{ MHz}$    | 3.5 dB Coarse gain |         | 70.4        |     |      | 57       |     |          |

|                                                          | F <sub>in</sub> = 10 MHz      |                    |         | 74.9        |     |      |          |     |          |

|                                                          | F <sub>in</sub> = 50 MHz      |                    |         | 74.4        |     |      |          |     |          |

| SINAD                                                    | F <sub>in</sub> = 70 MHz      |                    | 67      | 74.4        |     | 64   | 74       |     |          |

| Signal-to-noise and distortion ratio                     | E 470 MH-                     | 0 dB Gain          |         | 72.4        |     |      |          |     | dBFS     |

| LVDS                                                     | $F_{in} = 170 \text{ MHz}$    | 3.5 dB Coarse gain |         | 71.9        |     |      |          |     |          |

|                                                          | E 000 MIL                     | 0 dB Gain          |         | 70.5        |     |      | 56       |     |          |

|                                                          | $F_{in} = 230 \text{ MHz}$    | 3.5 dB Coarse gain |         | 70.5        |     |      |          |     |          |

| ENOB                                                     | F <sub>in</sub> = 50 MHz      | +                  |         |             |     |      |          |     | <b>.</b> |

| Effective number of bits                                 | F <sub>in</sub> = 70 MHz      |                    | 10.5    | 12          |     | 9.4  | 12       |     | Bits     |

|                                                          | F <sub>in</sub> = 10 MHz      |                    |         | 95          |     |      |          |     |          |

|                                                          | F <sub>in</sub> = 50 MHz      |                    |         | 89          |     |      |          |     |          |

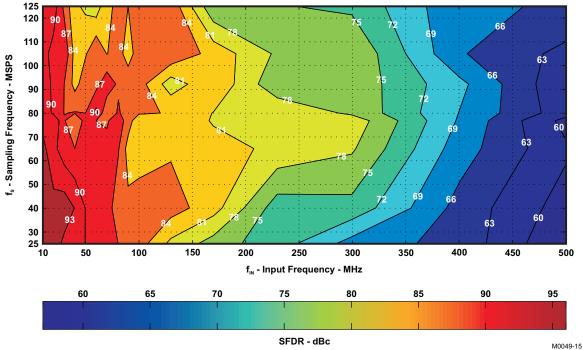

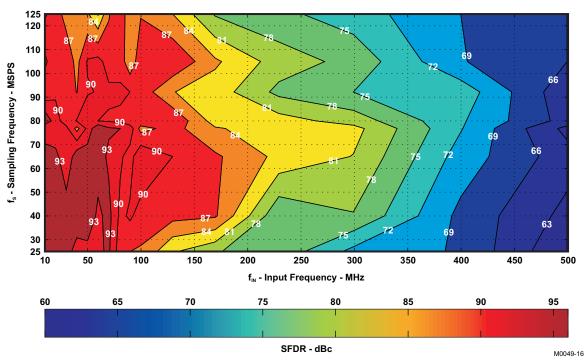

| SFDR                                                     | F <sub>in</sub> = 70 MHz      |                    | 70      | 78          |     | 66   | 77       |     |          |

| Spurious free dynamic                                    |                               | 0 dB Gain          |         | 82          |     |      |          |     | dBc      |

| range                                                    | F <sub>in</sub> = 170 MHz     | 3.5 dB Coarse gain |         | 84          |     |      |          |     |          |

|                                                          |                               | 0 dB Gain          |         | 79          |     |      | 58       |     |          |

|                                                          | $F_{in} = 230 \text{ MHz}$    | 3.5 dB Coarse gain |         | 82          |     |      | 60       |     |          |

|                                                          | F <sub>in</sub> = 10 MHz      |                    |         | 93          |     |      |          |     |          |

|                                                          | F <sub>in</sub> = 50 MHz      |                    |         | 88          |     |      |          |     |          |

|                                                          | F <sub>in</sub> = 70 MHz      |                    | 72      | 85          |     | 66   | 75       |     |          |

| THD                                                      |                               | 0 dB Gain          |         | 80          |     |      |          |     | dBc      |

| Total harmonic distortion                                | $F_{in} = 170 \text{ MHz}$    | 3.5 dB Coarse gain |         | 82          |     |      |          |     |          |

|                                                          |                               | 0 dB Gain          |         | 76          |     |      | 56       |     |          |

|                                                          | $F_{in} = 230 \text{ MHz}$    | 3.5 dB Coarse gain |         | 78.5        |     |      | 59       |     |          |

## **ELECTRICAL CHARACTERISTICS (continued)**

Typical values are at 25°C, AVDD = DRVDD = 3.3 V, maximum rated sampling frequency, 50% clock duty cycle, -1 dBFS differential analog input, internal reference mode, applies to CMOS and LVDS interfaces, unless otherwise noted.

| PARAMETER                                   | TEST CONDITIONS                                                               |                    | Tj = -4 | 0°C to 125° | °C  | Tj  | = 210°C |     | UNIT            |

|---------------------------------------------|-------------------------------------------------------------------------------|--------------------|---------|-------------|-----|-----|---------|-----|-----------------|

| PARAMETER                                   | IES                                                                           | of CONDITIONS      | MIN     | TYP         | MAX | MIN | TYP     | MAX | UNII            |

|                                             | F <sub>in</sub> = 10 MHz                                                      |                    |         | 98          |     |     |         |     |                 |

|                                             | F <sub>in</sub> = 50 MHz                                                      |                    |         | 96          |     |     |         |     |                 |

| HD2                                         | F <sub>in</sub> = 70 MHz                                                      |                    | 73      | 93          |     | 66  | 76      |     |                 |

| Second harmonic                             | F 470 MH-                                                                     | 0 dB Gain          |         | 86          |     |     |         |     | dBc             |

| distortion                                  | F <sub>in</sub> = 170 MHz                                                     | 3.5 dB Coarse gain |         | 87          |     |     |         |     |                 |

|                                             | F <sub>in</sub> = 230 MHz                                                     | 0 dB Gain          |         | 79          |     |     | 58      |     |                 |

|                                             | F <sub>in</sub> = 230 IVITZ                                                   | 3.5 dB Coarse gain |         | 81          |     |     | 60      |     |                 |

|                                             | F <sub>in</sub> = 10 MHz                                                      |                    |         | 95          |     |     |         |     |                 |

|                                             | F <sub>in</sub> = 50 MHz                                                      |                    |         | 89          |     |     |         |     |                 |

| HD3<br>Third harmonic<br>distortion         | F <sub>in</sub> = 70 MHz                                                      |                    | 75      | 86          |     | 70  | 84      |     |                 |

|                                             | F <sub>in</sub> = 170 MHz                                                     | 0 dB Gain          |         | 82          |     |     |         |     | dBc             |

|                                             | F <sub>in</sub> = 170 MHZ                                                     | 3.5 dB Coarse gain |         | 84          |     |     |         |     |                 |

|                                             | E 220 MH=                                                                     | 0 dB Gain          |         | 79          |     |     | 75      |     |                 |

|                                             | F <sub>in</sub> = 230 MHz                                                     | 3.5 dB Coarse gain |         | 82          |     |     | 74      |     |                 |

|                                             | F <sub>in</sub> = 10 MHz                                                      |                    |         | 97          |     |     |         |     |                 |

|                                             | F <sub>in</sub> = 50 MHz                                                      |                    |         | 96          |     |     |         |     |                 |

| Worst spur (other than HD2, HD3)            | F <sub>in</sub> = 70 MHz                                                      |                    |         | 95          |     |     |         |     | dBc             |

| 52,50)                                      | F <sub>in</sub> = 170 MHz                                                     |                    | 91      |             |     |     |         |     |                 |

|                                             | F <sub>in</sub> = 230 MHz                                                     |                    |         | 90          |     |     |         |     |                 |

| IMD<br>2-Tone intermodulation<br>distortion | F1 = 185 MHz, F2 = 190 MHz,<br>Each tone at -7 dBFS                           |                    |         | 91          |     |     | 90      |     | dBFS            |

| Input overload recovery                     | Recovery to within 3% (of final value) for 6-dB overload with sine wave input |                    |         | 1           |     |     | 1       |     | clock<br>cycles |

| PSRR<br>AC Power supply<br>rejection ratio  | For 100 mVpp sign                                                             | nal on AVDD supply |         | 49          |     |     | 48      |     | dBc             |

## **DIGITAL CHARACTERISTICS**

The dc specifications refer to the condition where the digital outputs are not switching, but are permanently at a valid logic level 0 or 1, AVDD = 3.3 V

|                 | PARAMETER                           | TEST CONDITIONS                                                    | Tj = -40°0 | Tj = -40°C to 85°C |     |     | = 210°C |     | UNIT |

|-----------------|-------------------------------------|--------------------------------------------------------------------|------------|--------------------|-----|-----|---------|-----|------|

|                 | PARAMETER                           | TEST CONDITIONS                                                    | MIN        | TYP                | MAX | MIN | TYP     | MAX | UNII |

|                 | L INPUTS<br>CLK, SDATA, and SEN     | (1)                                                                |            |                    |     |     |         |     |      |

|                 | High-level input voltage            |                                                                    | 2.4        |                    |     | 2.4 |         |     | V    |

|                 | Low-level input voltage             |                                                                    |            |                    | 0.8 |     |         | 8.0 | V    |

|                 | High-level input current            |                                                                    |            | 33                 |     |     | 33      |     | μΑ   |

|                 | Low-level input current             |                                                                    |            | -33                |     |     | -33     |     | μΑ   |

|                 | Input capacitance                   |                                                                    |            | 4                  |     |     | 4       |     | pF   |

|                 | L OUTPUTS<br>INTERFACE, DRVDD = 1   | I.8 to 3.3 V                                                       |            |                    |     |     |         |     |      |

|                 | High-level output voltage           |                                                                    | DR         | VDD                |     |     | DRVDD   |     | V    |

|                 | Low-level output voltage            |                                                                    |            | 0                  |     |     | 0       |     | V    |

|                 | Output capacitance                  | Output capacitance inside the device, from each output to ground   |            | 2                  |     |     | 2       |     | pF   |

|                 | L OUTPUTS<br>NTERFACE, DRVDD = 3    | .3 V, $I_0$ = 3.5 mA, $R_L$ = 100 $\Omega$ <sup>(2)</sup>          |            |                    |     |     |         |     |      |

|                 | High-level output voltage           |                                                                    |            | 1375               |     |     | 1375    |     | mV   |

|                 | Low-level output voltage            |                                                                    |            | 1025               |     |     | 1025    |     | mV   |

| V <sub>OD</sub> | Output differential voltage         |                                                                    | 225        | 350                |     | 225 | 350     |     | mV   |

| Vos             | Output offset voltage, single-ended | Common-mode voltage of OUTP, OUTM                                  |            | 1200               |     |     | 1200    |     | mV   |

|                 | Output capacitance                  | Output capacitance inside the device, from either output to ground |            | 2                  |     |     | 2       |     | pF   |

<sup>(1)</sup> SCLK and SEN function as digital input pins when they are used for serial interface programming. When used as parallel control pins, analog voltage needs to be applied as per Table 3 & Table 4

(2) I<sub>O</sub> Refers to the LVDS buffer current setting, R<sub>L</sub> is the differential load resistance between the LVDS output pair.

ZHCS611 – DECEMBER 2011 www.ti.com.cn

## TEXAS INSTRUMENTS

## TIMING CHARACTERISTICS – LVDS AND CMOS MODES(1)

Typical values are at 25°C, min and max values are across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 125$ °C or 210°C as indicated, AVDD = DRVDD = 3.3 V, maximum rated sampling frequency, sine wave input clock, 1.5  $V_{PP}$  clock amplitude,  $C_L = 5 \ pF^{(2)}$ ,  $I_O = 3.5 \ mA$ ,  $R_L = 100 \ \Omega^{(3)}$ , no internal termination, unless otherwise noted.

For timings at lower sampling frequencies, see section Output Timings in the APPLICATION INFORMATION of this data sheet.

|                                              | DADAMETER                                         | TEOT CONST                                                                                         | TIONS                                               | Tj = -5         | 5°C to 125°C | ;   | Tj  | j = 210°C |     | T.11411.T    |

|----------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------|--------------|-----|-----|-----------|-----|--------------|

| ,                                            | PARAMETER                                         | TEST CONDI                                                                                         | IIONS                                               | MIN             | TYP          | MAX | MIN | TYP       | MAX | UNIT         |

| t <sub>a</sub>                               | Aperture delay                                    |                                                                                                    |                                                     |                 | 1.5          |     |     |           |     | ns           |

| t <sub>j</sub>                               | Aperture jitter                                   |                                                                                                    |                                                     |                 | 150          |     |     |           |     | fs rms       |

|                                              |                                                   | From global power do                                                                               | own                                                 |                 | 15           |     |     |           |     | μs           |

|                                              | Wake-up time                                      | From standby                                                                                       |                                                     |                 | 15           |     |     |           |     | μs           |

|                                              | (to valid data)                                   | From output buffer                                                                                 | CMOS                                                |                 | 100          |     |     |           |     | ns           |

|                                              |                                                   | disable                                                                                            | LVDS                                                |                 | 200          |     |     |           |     | ns           |

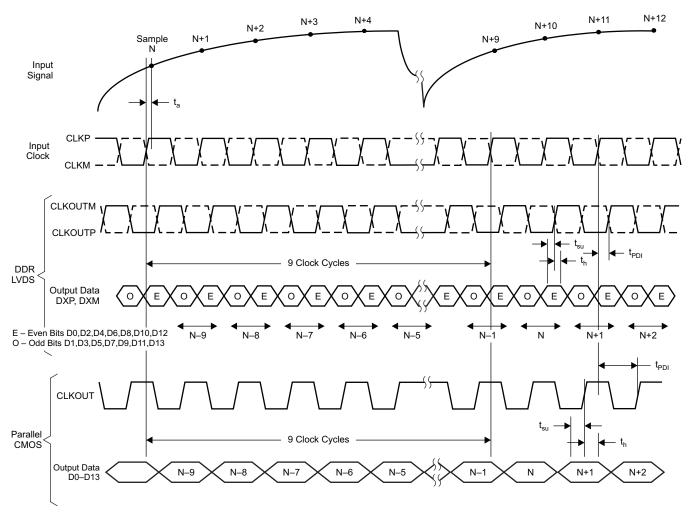

|                                              | Latency                                           |                                                                                                    |                                                     |                 | 9            |     |     |           |     | clock cycles |

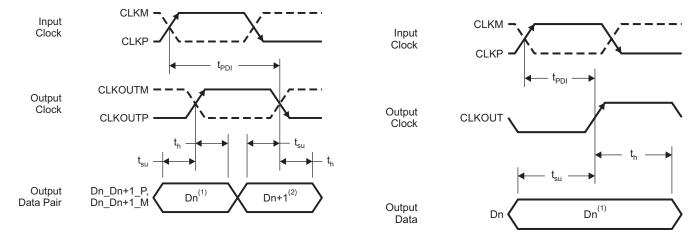

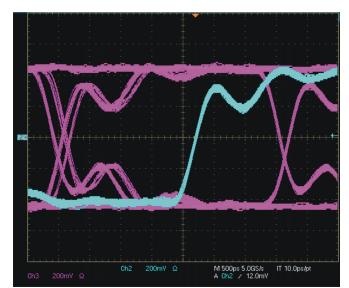

| DDR LVI                                      | DS MODE <sup>(4)</sup> , DRVDD                    | = 3.3 V                                                                                            |                                                     |                 |              | ·   |     |           |     |              |

| t <sub>su</sub>                              | Data setup time <sup>(5)</sup>                    | Data valid <sup>(6)</sup> to zero-<br>CLKOUTP                                                      | cross of                                            |                 | 5.8          |     |     | 5.6       |     | ns           |

| t <sub>h</sub>                               | Data hold time <sup>(5)</sup>                     | Zero-cross of CLKOUTP to data becoming invalid (6)                                                 |                                                     |                 | 1.3          |     |     | 1.5       |     | ns           |

| t <sub>PDI</sub>                             | Clock propagation delay                           | Input clock rising edg<br>to output clock rising<br>zero-cross                                     |                                                     |                 | 6.2          |     |     | 7.2       |     | ns           |

|                                              | LVDS bit clock<br>duty cycle                      | Duty cycle of differen (CLKOUTP-CLKOUT $10 \le F_s \le 125 \text{ MSPS}$                           |                                                     |                 | 46%          |     |     | 46%       |     |              |

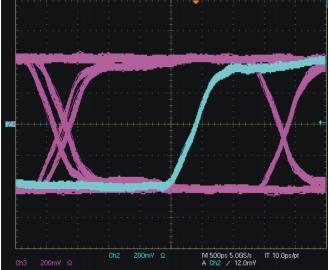

| t <sub>r</sub><br>t <sub>f</sub>             | Data rise time,<br>Data fall time                 | Rise time measured to 50 mV,<br>Fall time measured fr<br>to $-50$ mV,<br>$1 \le F_s \le 125$ MSPS  |                                                     | 112             |              | 116 |     |           | ps  |              |

| t <sub>CLKRISE</sub><br>t <sub>CLKFALL</sub> | Output clock rise time,<br>Output clock fall time | to 50 mV,                                                                                          | measured from –50 mV neasured from 50 mV 112 5 MSPS |                 |              | 116 |     |           | ps  |              |

| PARALL                                       | EL CMOS MODE, DR                                  | <b>RVDD</b> = 2.5 V to 3.3 V,                                                                      | default output                                      | buffer drive st | rength (7)   |     |     |           |     |              |

| t <sub>su</sub>                              | Data setup time <sup>(5)</sup>                    | Data valid <sup>(8)</sup> to 50% or rising edge                                                    | of CLKOUT                                           |                 | 8            |     |     | 9         |     | ns           |

| t <sub>h</sub>                               | Data hold time <sup>(5)</sup>                     | 50% of CLKOUT rising data becoming invalid                                                         |                                                     |                 | 6.5          |     |     | 6.8       |     | ns           |

| t <sub>PDI</sub>                             | Clock propagation delay                           | Input clock rising edg<br>to 50% of CLKOUT ri                                                      |                                                     |                 | 7.3          |     |     | 8.3       |     | ns           |

|                                              | Output clock duty cycle                           | Duty cycle of output clock (CLKOUT),<br>10 ≤ F <sub>s</sub> ≤ 125 MSPS                             |                                                     | 42%             |              |     |     | 42%       |     |              |

| t <sub>r</sub><br>t <sub>f</sub>             | Data rise time,<br>Data fall time                 | 80% of DRVDD,                                                                                      | ime measured from 80% to of DRVDD,                  |                 |              |     | 2.1 |           |     | ns           |

| t <sub>CLKRISE</sub><br>t <sub>CLKFALL</sub> | Output clock rise time,<br>Output clock fall time | Rise time measured to 80% of DRVDD, Fall time measured from 20% of DRVDD, $1 \le F_s \le 125$ MSPS |                                                     |                 | 1.9          |     |     | 2.1       |     | ns           |

- (1) Timing parameters are specified by design and not tested in production.

- (2) C<sub>L</sub> is the Effective external single-ended load capacitance between each output pin and ground.

- (3) Io Refers to the LVDS buffer current setting; R<sub>L</sub> is the differential load resistance between the LVDS output pair.

- 4) Measurements are done with a transmission line of 100 Ω characteristic impedance between the device and the load.

- (5) Setup and hold time specifications take into account the effect of jitter on the output data and clock.

- (6) Data valid refers to a logic high of +100 mV and logic low of -100 mV.

- (7) For DRVDD < 2.2 V, it is recommended to use an external clock for data capture and NOT the device output clock signal (CLKOUT). See Parallel CMOS interface in the application section.

- (8) Data valid refers to a logic high of 2  $\dot{V}$  (1.7 V) and logic low of 0.8 V (0.7 V) for DRVDD = 3.3 V (2.5 V).

www.ti.com.cn ZHCS611 – DECEMBER 2011

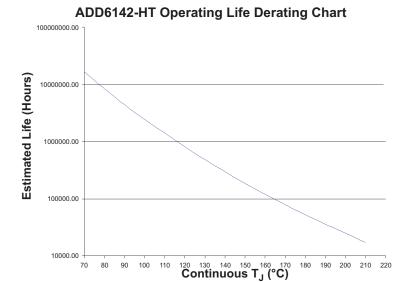

- (1) See data sheet for absolute maximum and minimum recommended operating conditions.

- (2) Silicon operating life design goal is 10 years at 105°C junction temperature (does not include package interconnect life).

- (3) The predicted operating lifetime vs. junction temperature is based on reliability modeling using electromigration as the dominant failure mechanism affecting device wearout for the specific device process and design characteristics.

Figure 1. ADS6142-HT Operating Life Derating Chart

Figure 2. Latency

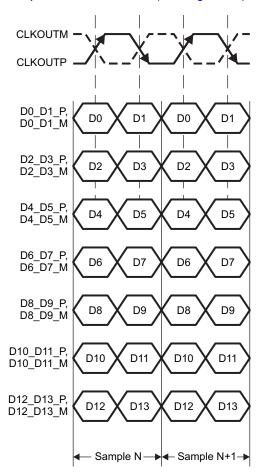

<sup>&</sup>lt;sup>(1)</sup>Dn — Bits D0, D2, D4, D6, D8, D10, D12 <sup>(2)</sup>Dn+1 — Bits D1, D3, D5, D7, D9, D11, D13

Figure 3. LVDS Mode Timing

<sup>(1)</sup>Dn – Bits D0–D13

Figure 4. CMOS Mode Timing

DEVICE DROOP A MANUAL MODE

#### DEVICE PROGRAMMING MODES

The ADS6142 has several features that can be easily configured using either parallel interface control or serial interface programming.

#### USING SERIAL INTERFACE PROGRAMMING ONLY

To program using the serial interface, the internal registers must first be reset to their default values, and the RESET pin must be kept *low*. In this mode, SEN, SDATA, and SCLK function as serial interface pins and are used to access the internal registers of the ADC. The registers are reset either by applying a pulse on the RESET pin or by a *high* setting on the <RST> bit (D4 in register 0x00). The Serial Interface section describes register programming and register reset in more detail.

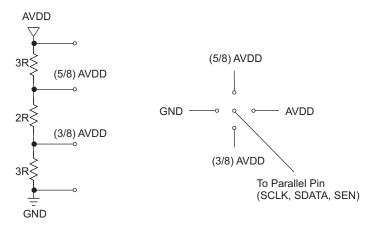

#### **USING PARALLEL INTERFACE CONTROL ONLY**

To control the device using the parallel interface, keep RESET tied *high* (AVDD). Now SEN, SCLK, SDATA, and PDN function as parallel interface control pins. These pins can be used to directly control certain modes of the ADC by connecting them to the correct voltage levels (as described in Table 3 to Table 5). There is no need to apply a reset pulse.

Frequently used functions are controlled in this mode — standby, selection between LVDS/CMOS output format, internal/external reference, and 2s complement/straight binary output format.

Figure 5. Simple Scheme to Configure Parallel Pins

#### DESCRIPTION OF PARALLEL PINS

#### Table 3. SCLK (Analog Control Pin)

| SCLK       | DESCRIPTION                                                                    |  |  |  |  |

|------------|--------------------------------------------------------------------------------|--|--|--|--|

| 0          | 0 Internal reference and 0 dB gain (full-scale = 2 V <sub>PP</sub> )           |  |  |  |  |

| (3/8) AVDD | (3/8) AVDD External reference and 0 dB gain (full-scale = 2 V <sub>PP</sub> )  |  |  |  |  |

| (5/8) AVDD | External reference and 3.5 dB coarse gain (full-scale = 1.34 V <sub>PP</sub> ) |  |  |  |  |

| AVDD       | Internal reference and 3.5 dB coarse gain (full-scale = 1.34 V <sub>PP</sub> ) |  |  |  |  |

#### Table 4. SEN (Analog Control Pin)

| SEN        | DESCRIPTION                                      |

|------------|--------------------------------------------------|

| 0          | 2s Complement format and DDR LVDS interface      |

| (3/8) AVDD | Straight binary format and DDR LVDS interface    |

| (5/8) AVDD | Straight binary and parallel CMOS interface      |

| AVDD       | 2s Complement format and parallel CMOS interface |

ZHCS611 – DECEMBER 2011 www.ti.com.cn

| SDATA       | PDN         | DESCRIPTION                                                                                        |

|-------------|-------------|----------------------------------------------------------------------------------------------------|

| Low         | Low         | Normal operation                                                                                   |

| Low         | High (AVDD) | Standby - only the ADC is powered down                                                             |

| High (AVDD) | Low         | Output buffers are powered down, fast wake-up time                                                 |

| High (AVDD) | High (AVDD) | Global power down. ADC, internal reference, and output buffers are powered down, slow wake-up time |

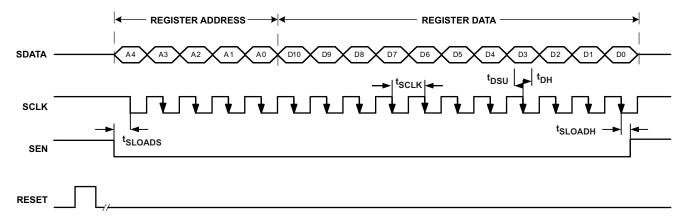

#### SERIAL INTERFACE

The ADC has a set of internal registers, which can be accessed through the serial interface formed by pins SEN (Serial interface Enable), SCLK (Serial Interface Clock), SDATA (Serial Interface Data) and RESET. After device power-up, the internal registers must be reset to their default values by applying a high-going pulse on RESET (of width greater than 10 ns).

Serial shift of bits into the device is enabled when SEN is low. Serial data SDATA is latched at every falling edge of SCLK when SEN is active (low). The serial data is loaded into the register at every 16th SCLK falling edge when SEN is low. If the word length exceeds a multiple of 16 bits, the excess bits are ignored. Data is loaded in multiples of 16-bit words within a single active SEN pulse.

The first 5 bits form the register address and the remaining 11 bits form the register data.

The interface can work with a SCLK frequency from 20 MHz down to very low speeds (a few hertz) and also with a non-50% SCLK duty cycle.

Figure 6. Serial Interface Timing Diagram

#### **REGISTER INITIALIZATION**

After power-up, the internal registers *must* be reset to their default values. This is done in one of two ways:

1. Either through a hardware reset by applying a high-going pulse on the RESET pin (width greater than 10 ns) as shown in Figure 6.

OR

2. By applying a software reset. Using the serial interface, set the <RST> bit (D4 in register 0x00) to *high*. This initializes the internal registers to their default values and then self-resets the <RST> bit to *low*. In this case the RESET pin is kept *low*.

## **SERIAL INTERFACE TIMING**

Typical values at 25°C, min and max values across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 210$ °C, AVDD = DRVDD = 3.3 V (unless otherwise noted)

|                     |                                      | MIN  | TYP MAX | UNIT |

|---------------------|--------------------------------------|------|---------|------|

| f <sub>SCLK</sub>   | SCLK Frequency = 1/t <sub>SCLK</sub> | > DC | 20      | MHz  |

| t <sub>SLOADS</sub> | SEN to SCLK Setup time               | 25   |         | ns   |

| t <sub>SLOADH</sub> | SCLK to SEN Hold time                | 25   |         | ns   |

| t <sub>DSU</sub>    | SDATA Setup time                     | 25   |         | ns   |

| t <sub>DH</sub>     | SDATA Hold time                      | 25   |         | ns   |

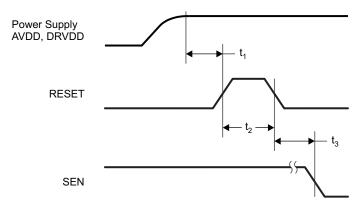

#### **RESET TIMING**

Typical values at 25°C, min and max values across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, AVDD = DRVDD = 3.3 V (unless otherwise noted)

|                 | PARAMETER            | TEST CONDITIONS                                             | MIN | TYP | MAX | UNIT |

|-----------------|----------------------|-------------------------------------------------------------|-----|-----|-----|------|

| t <sub>1</sub>  | Power-on delay       | Delay from power-up of AVDD and DRVDD to RESET pulse active | 5   |     |     | ms   |

| t <sub>2</sub>  | Reset pulse width    | Pulse width of active RESET signal                          | 10  |     |     | ns   |

| t <sub>3</sub>  | Register write delay | Delay from RESET disable to SEN active                      | 25  |     |     | ns   |

| t <sub>PO</sub> | Power-up time        | Delay from power-up of AVDD and DRVDD to output stable      |     | 6.5 |     | ms   |

NOTE: A high-going pulse on the RESET pin is required in serial interface mode in the case of initialization through a hardware reset. For parallel interface operation, RESET has to be tied permanently HIGH.

Figure 7. Reset Timing Diagram

## **ISTRUMENTS**

#### **SERIAL REGISTER MAP**

Table 6 gives a summary of all the modes that can be programmed through the serial interface.

Table 6. Summary of Functions Supported by Serial Interface<sup>(1)</sup> (2)

| REGISTER<br>ADDRESS<br>IN HEX |                                                                         |                                                                       |                                                         |                                                                                                         | REGIS         | TER FUNCT                                              | IONS                               |    |                                                        |    |                                      |

|-------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------|------------------------------------|----|--------------------------------------------------------|----|--------------------------------------|

| A4 - A0                       | D10                                                                     | D9                                                                    | D8                                                      | D7                                                                                                      | D6            | D5                                                     | D4                                 | D3 | D2                                                     | D1 | D0                                   |

| 00                            | <pdn obuf=""> Output buffers powered down</pdn>                         | <coarse gain=""> Coarse gain</coarse>                                 | <lvds cmos=""> LVDS or CMOS Output interface</lvds>     | 0                                                                                                       | 0             | <ref><br/>Internal or<br/>external<br/>Reference</ref> | <rst><br/>Software<br/>reset</rst> | 0  | <pdn clkout=""> Output clock buffer powered down</pdn> | 0  | <stby><br/>ADC Power<br/>down</stby> |

| 04                            | <pre><dataout posn=""> Output data position control</dataout></pre>     | <clkout<br>EDGE&gt;<br/>Output<br/>clock edge<br/>control</clkout<br> | <clkout posn=""> Output clock position control</clkout> | 0                                                                                                       | 0             | 0                                                      | 0                                  | 0  | 0                                                      | 0  | 0                                    |

| 09                            | Bit-wise or<br>Byte-wise<br>control                                     | 0                                                                     | 0                                                       | 0                                                                                                       | 0             | 0                                                      | 0                                  | 0  | 0                                                      | 0  | 0                                    |

| 0A                            | <pre><data format="">    2s Complemen t or straight binary</data></pre> | 0                                                                     | 0                                                       | <tes< td=""><td>ST PATTER</td><td>RNS&gt;</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td></tes<> | ST PATTER     | RNS>                                                   | 0                                  | 0  | 0                                                      | 0  | 0                                    |

| 0B                            |                                                                         |                                                                       |                                                         |                                                                                                         | oattern lower |                                                        |                                    |    |                                                        | 0  | 0                                    |

| 0C                            | F                                                                       | <fine gain:<br="">ine gain 0 to 6</fine>                              |                                                         | 0 0 CUSTOM HIGH> Custom pattern upper 5 bits                                                            |               |                                                        |                                    |    |                                                        |    |                                      |

| 0E                            | 0                                                                       | LVDS Termination                                                      |                                                         |                                                                                                         |               |                                                        |                                    |    |                                                        | DC | JRRENT<br>DUBLE><br>urrent double    |

| 0F                            | 0                                                                       | 0                                                                     | 0                                                       | CMOS                                                                                                    |               | STRENGTH:<br>er drive stren                            |                                    | 0  | 0                                                      | 0  | 0                                    |

<sup>(1)</sup> The unused bits in each register (shown by blank cells in above table) must be programmed as '0'.(2) Multiple functions in a register can be programmed in a single write operation.

## **DESCRIPTION OF SERIAL REGISTERS**

Each register function is explained in detail.

#### Table 7.

| A4-A0<br>(hex) | D10                                                                                                                                               | D9                                                                                         | D8                                                          | D7        | D6     | D5                                         | D4                                 | D3    | D2                                                     | D1 | D0                                   |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------|--------|--------------------------------------------|------------------------------------|-------|--------------------------------------------------------|----|--------------------------------------|--|

| 00             | <pdn obuf=""> Output buffers powered down</pdn>                                                                                                   |                                                                                            | <lvds cmos=""><br/>LVDS or CMOS<br/>Output interface</lvds> | 0         | 0      | <ref> Internal or external reference</ref> | <rst><br/>Software<br/>reset</rst> | 0     | <pdn clkout=""> Output clock buffer powered down</pdn> | 0  | <stby><br/>ADC Power<br/>down</stby> |  |

|                | 00 <s< th=""><th colspan="11"><stby> Power down modes</stby></th></s<>                                                                            | <stby> Power down modes</stby>                                                             |                                                             |           |        |                                            |                                    |       |                                                        |    |                                      |  |

|                | 0 Noi                                                                                                                                             | mal operation                                                                              | on                                                          |           |        |                                            |                                    |       |                                                        |    |                                      |  |

|                | 1 Dev                                                                                                                                             | vice enters s                                                                              | tandby mode v                                               | vhere or  | ıly Al | DC is powe                                 | ered dow                           | n.    |                                                        |    |                                      |  |

|                | )2 <pi< th=""><th>ON CLKOUT</th><th>Γ&gt; Power down</th><th>modes</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></pi<>      | ON CLKOUT                                                                                  | Γ> Power down                                               | modes     |        |                                            |                                    |       |                                                        |    |                                      |  |

|                | 0 Out                                                                                                                                             | tput clock is                                                                              | active (on CLK                                              | OUT pir   | າ)     |                                            |                                    |       |                                                        |    |                                      |  |

|                | 1 Out                                                                                                                                             | Output clock buffer is powered down and becomes three-stated. Data outputs are unaffected. |                                                             |           |        |                                            |                                    |       |                                                        |    |                                      |  |

|                | 04 <r< th=""><th colspan="9"><rst></rst></th><th></th></r<>                                                                                       | <rst></rst>                                                                                |                                                             |           |        |                                            |                                    |       |                                                        |    |                                      |  |

|                | 1 Sof                                                                                                                                             | tware reset                                                                                | applied - resets                                            | all inte  | rnal r | registers ar                               | nd the bit                         | self- | clears to 0.                                           |    |                                      |  |

|                | 05 <r< th=""><th>EF&gt; Referer</th><th>ce selection</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></r<>            | EF> Referer                                                                                | ce selection                                                |           |        |                                            |                                    |       |                                                        |    |                                      |  |

| -              | 0 Inte                                                                                                                                            | rnal referen                                                                               | ce enabled                                                  |           |        |                                            |                                    |       |                                                        |    |                                      |  |