Technical documentation

Support & training

**DRV8962** ZHCSLY0 - AUGUST 2022

# DRV8962 具有电流检测输出的四通道半桥驱动器

# 1 特性

- 四通道半桥驱动器 ٠

- 独立控制每个半桥

- 4.5V 至 65V 工作电源电压范围

- 低 R<sub>DS(ON)</sub>:每个 FET 50m Q (24V, 25°C)

- 高电流容量:

- DDW 封装: 高达 5A/每输出

- DDV 封装: 高达 10A/每输出

- 可驱动各种类型的负载-

- 高达四个电磁阀负载

- 一个步进电机

- 两个有刷直流电机

- 一个或两个热电冷却器 (TEC)

- 一个三相无刷直流电机

- 一个三相永磁同步电机 (PMSM)

- 集成式电流检测和调节

- 高侧 MOSFET 上的电流检测

- 每个半桥的感应输出 (IPROPI)

- 最大电流下的检测精度**±4%**

- 可选外部检测电阻

- 与以下器件引脚对引脚兼容:

- DRV8952:48V 四通道半桥驱动器

- 单独的逻辑电源电压 (VCC)

- 可编程输出下降/上升时间

- 可编程故障恢复方法

- 支持 1.8V、3.3V、5.0V 逻辑输入 ٠

- 低电流睡眠模式 (3µA) •

- 保护特性 ٠

- VM 欠压锁定 (UVLO)

- 电荷泵欠压 (CPUV)

- 过流保护 (OCP)

- 热关断 (OTSD)

- 故障状态输出 (nFAULT)

# 2 应用

- 工厂自动化、步进驱动器和机器人

- 医疗成像、诊断和设备

- 舞台照明

- PLC

- TEC 驱动器

- BLDC 电机模块

- 有刷直流和步进电机驱动器

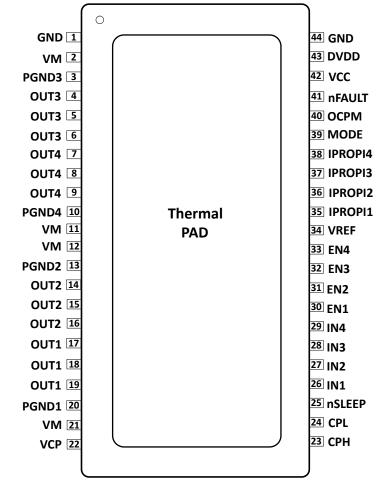

# 3 说明

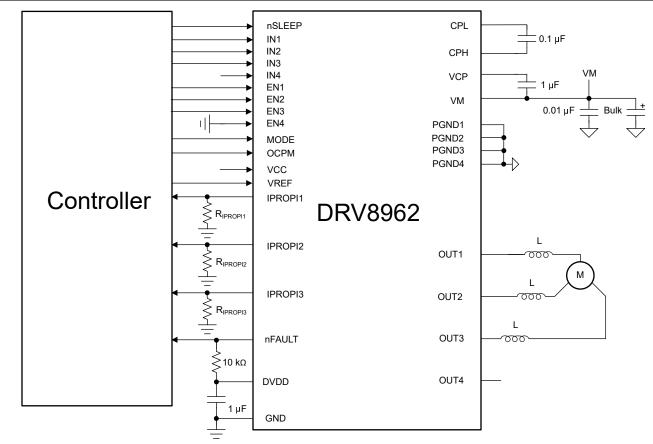

DRV8962 是一款宽电压、高功率、四通道半桥驱动 器,适用于各种工业应用。该器件支持高达 65V 的电 源电压;具有 50m Ω 导通电阻的集成式 MOSFET 允 许 DDW 封装的每输出产生高达 5A 的电流,允许 DDV 封装的每输出产生高达 10A 的电流。

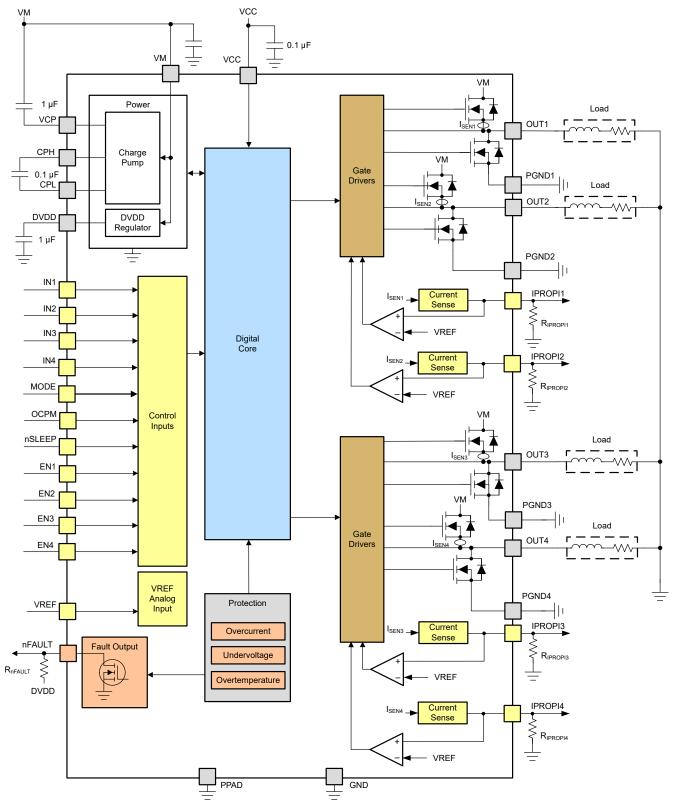

该器件可用于驱动最多四个螺线管负载、一个步进电 机、两个有刷直流电机、一个 BLDC 或 PMSM 电机以 及最多两个热电冷却器(珀耳帖元件)。器件的输出级 包括配置为四个独立半桥的 N 沟道功率 MOSFET、电 荷泵稳压器、电流检测和调节电路、电流检测输出以及 保护电路。

高侧 MOSFET 上的集成电流检测功能可让器件在负载 从输出端接地时调节电流。利用可调外部电压基准 (VREF),可设置调节电流限值。此外,该器件还提供 四个比例电流输出引脚,每个引脚对应一个半桥高侧 FET。可选的外部检测电阻也可从 PGND 引脚连接到 系统地。

该器件提供一种低功耗睡眠模式,可实现超低静态电 流。提供的内部保护特性包括:电源欠压锁定 (UVLO)、电荷泵欠压 (CPUV) 保护、输出过流 (OCP) 保护和器件过热 (OTSD) 保护。

|             | 器件信息                  |              |

|-------------|-----------------------|--------------|

| 器件型号        | 封装 <sup>(1)</sup>     | 封装尺寸 (标称值)   |

| DRV8962DDWR | HTSSOP (44),底部<br>裸焊盘 | 14mm x 6.1mm |

| DRV8962DDVR | HTSSOP (44),顶部<br>裸焊盘 | 14mm x 6.1mm |

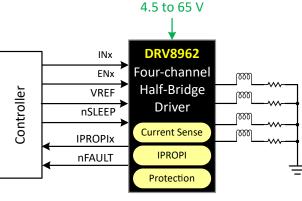

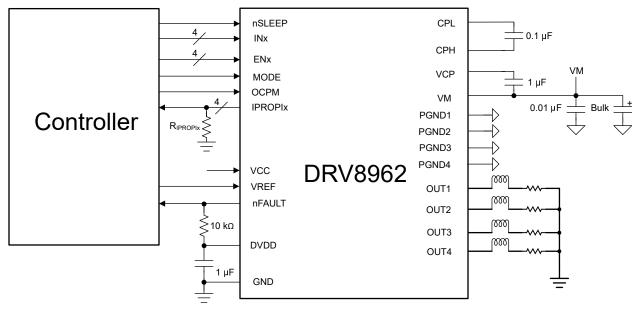

DRV8962 简化原理图

# **Table of Contents**

| 1 特性1                                   |

|-----------------------------------------|

| 2 应用                                    |

| 3 说明                                    |

| 4 Revision History                      |

| 5 Pin Configuration and Functions       |

| 6 Specifications                        |

| 6.1 Absolute Maximum Ratings6           |

| 6.2 ESD Ratings6                        |

| 6.3 Recommended Operating Conditions    |

| 6.4 Thermal Information7                |

| 6.5 Electrical Characteristics8         |

| 7 Detailed Description10                |

| 7.1 Overview10                          |

| 7.2 Functional Block Diagram11          |

| 7.3 Feature Description11               |

| 7.4 Independent Half-bridge Operation12 |

| 7.5 Current Sensing and Regulation13    |

| 7.6 Charge Pump16                       |

| 7.7 Linear Voltage Regulator17          |

| 7.8 VCC Voltage Supply 17               |

| 7.9 Logic Level Pin Diagram             |

| 7.10 Protection Circuits                |

| 7.11 Device Functional Modes20          |

| 8 Application and Implementation        | <mark>21</mark> |

|-----------------------------------------|-----------------|

| 8.1 Application Information             | <mark>21</mark> |

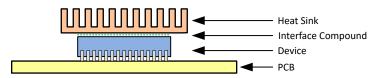

| 9 Package Thermal Considerations        | 33              |

| 9.1 DDW Package                         | 33              |

| 9.2 DDV Package                         |                 |

| 9.3 PCB Material Recommendation         | 34              |

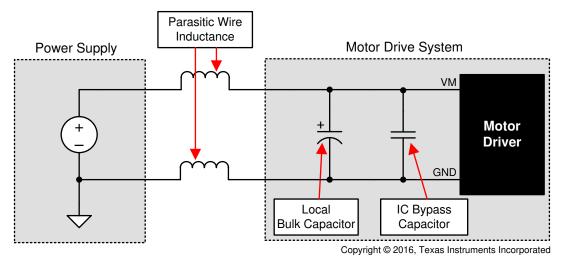

| 10 Power Supply Recommendations         | 35              |

| 10.1 Bulk Capacitance                   | 35              |

| 10.2 Power Supplies                     | 35              |

| 11 Layout                               | 37              |

| 11.1 Layout Guidelines                  |                 |

| 11.2 Layout Example                     | 37              |

| 12 Device and Documentation Support     | 38              |

| 12.1 Related Documentation              | 38              |

| 12.2 接收文档更新通知                           | 38              |

| 12.3 支持资源                               | 38              |

| 12.4 Trademarks                         | 38              |

| 12.5 Electrostatic Discharge Caution    | 38              |

| 12.6 术语表                                | 38              |

| 13 Mechanical, Packaging, and Orderable |                 |

| Information                             | 39              |

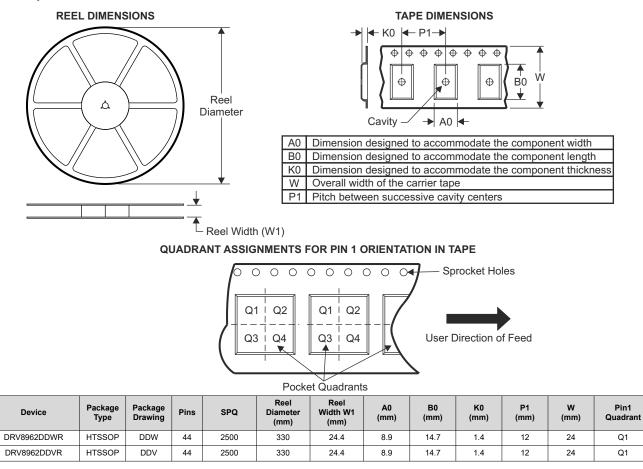

| 13.1 Tape and Reel Information          | 46              |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| 11. 以前放平的风码可能马 | コ前/灰平的火屿/115 |                 |

|----------------|--------------|-----------------|

| DATE           | REVISION     | NOTES           |

|                | *            | Initial Release |

# **5 Pin Configuration and Functions**

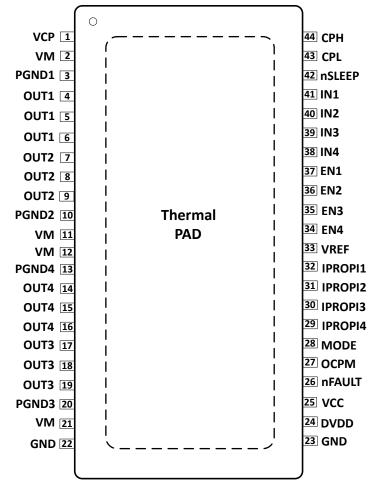

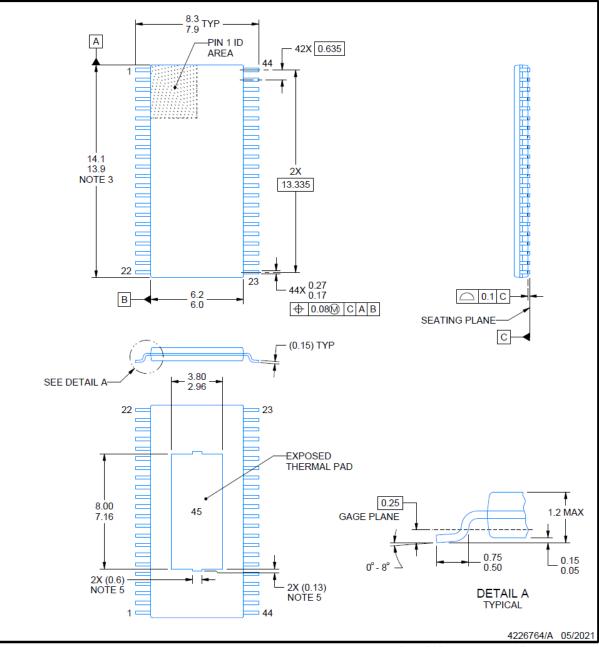

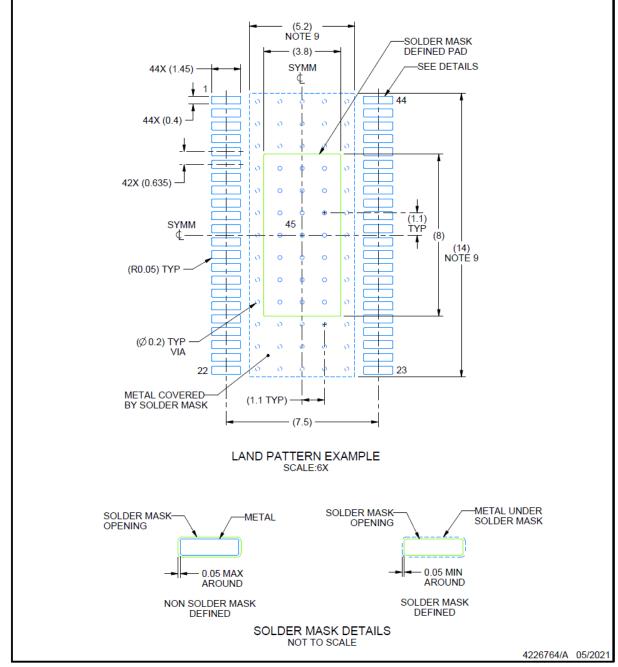

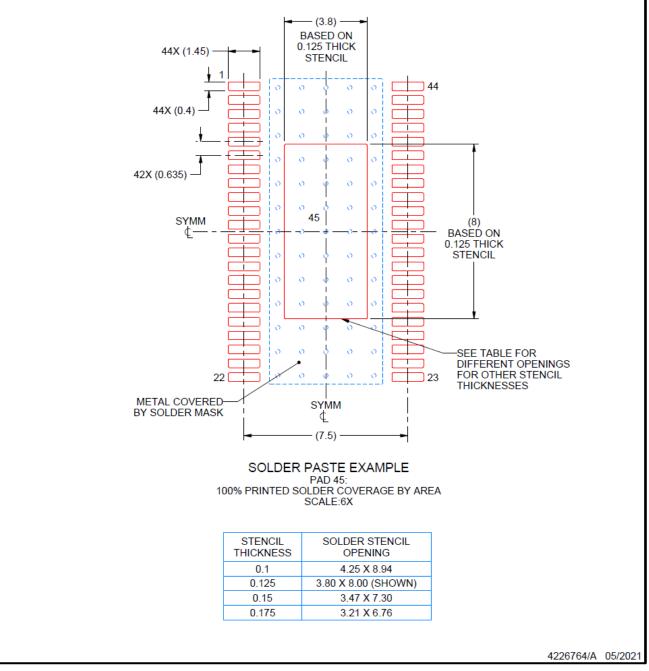

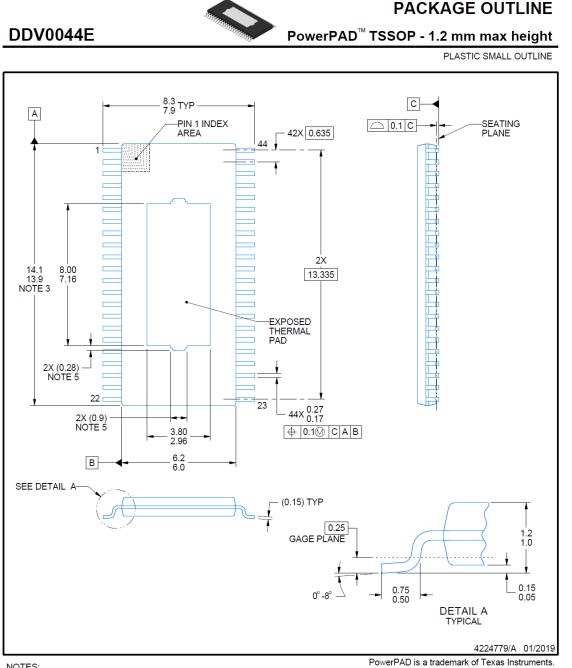

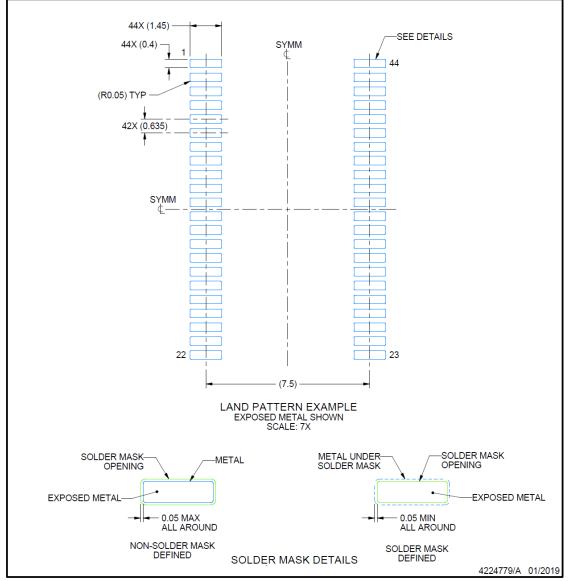

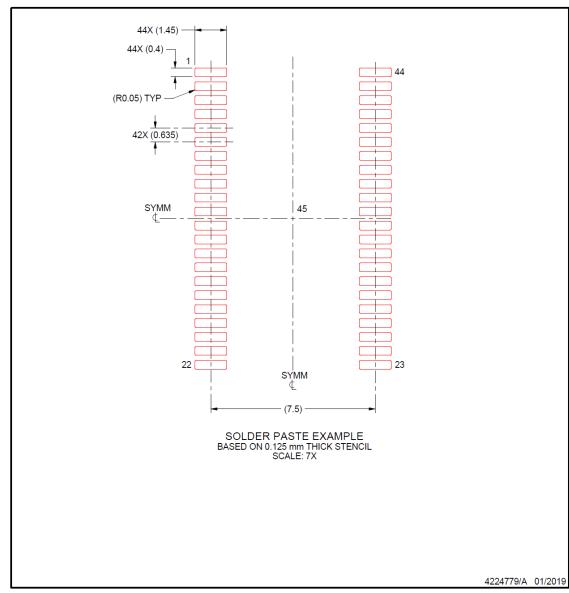

The DRV8962 is available in thermally-enhanced, 44-Pin HTSSOP packages.

- The DDW package contains a PowerPAD<sup>™</sup> on the bottom side of the device.

- The DDV package contains a PowerPAD<sup>™</sup> on the top side of the device for thermal coupling to a heatsink.

图 5-1. DDW Package, Top View

| PIN     |                  |                  | TYPE   | DESCRIPTION                                                                                                                                     |

|---------|------------------|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | DDW              | DDV              | TIPE   | DESCRIPTION                                                                                                                                     |

| VCP     | 1                | 22               | Power  | Charge pump output. Connect a X7R, 1- $\mu$ F, 16-V ceramic capacitor from VCP to VM.                                                           |

| VM      | 2, 11, 12,<br>21 | 2, 11, 12,<br>21 | Power  | Power supply. Connect to motor supply voltage and bypass to PGND pins with 0.01- $\mu$ F ceramic capacitors plus a bulk capacitor rated for VM. |

| PGND1   | 3                | 20               | Power  | Power ground for half-bridge 1. Connect to system ground.                                                                                       |

| PGND2   | 10               | 13               | Power  | Power ground for half-bridge 2. Connect to system ground.                                                                                       |

| PGND3   | 20               | 3                | Power  | Power ground for half-bridge 3. Connect to system ground.                                                                                       |

| PGND4   | 13               | 10               | Power  | Power ground for half-bridge 4. Connect to system ground.                                                                                       |

| OUT1    | 4, 5, 6          | 17, 18, 19       | Output | Connect to load terminal.                                                                                                                       |

| OUT2    | 7, 8, 9          | 14, 15, 16       | Output | Connect to load terminal.                                                                                                                       |

| OUT3    | 17, 18, 19       | 4, 5, 6          | Output | Connect to load terminal.                                                                                                                       |

| OUT4    | 14, 15, 16       | 7, 8, 9          | Output | Connect to load terminal.                                                                                                                       |

| IPROPI1 | 32               | 35               | Output | Current sense output for half-bridge 1.                                                                                                         |

| IPROPI2 | 31               | 36               | Output | Current sense output for half-bridge 2.                                                                                                         |

| IPROPI3 | 30               | 37               | Output | Current sense output for half-bridge 3.                                                                                                         |

| IPROPI4 | 29               | 38               | Output | Current sense output for half-bridge 4.                                                                                                         |

TEXAS INSTRUMENTS www.ti.com.cn

| PIN    |        |       | TYPE       | DECODIDION                                                                                                                                        |

|--------|--------|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | DDW    | DDV   | TYPE       | DESCRIPTION                                                                                                                                       |

| EN1    | 37     | 30    | Input      | Enable input of half-bridge 1.                                                                                                                    |

| EN2    | 36     | 31    | Input      | Enable input of half-bridge 2.                                                                                                                    |

| EN3    | 35     | 32    | Input      | Enable input of half-bridge 3.                                                                                                                    |

| EN4    | 34     | 33    | Input      | Enable input of half-bridge 4.                                                                                                                    |

| IN1    | 41     | 26    | Input      | PWM input for half-bridge 1.                                                                                                                      |

| IN2    | 40     | 27    | Input      | PWM input for half-bridge 2.                                                                                                                      |

| IN3    | 39     | 28    | Input      | PWM input for half-bridge 3.                                                                                                                      |

| IN4    | 38     | 29    | Input      | PWM input for half-bridge 4.                                                                                                                      |

| GND    | 22, 23 | 1, 44 | Power      | Device ground. Connect to system ground.                                                                                                          |

| СРН    | 44     | 23    | Power      | Charge pump switching node. Connect a X7R, 0.022- μ F, VM rated                                                                                   |

| CPL    | 43     | 24    | TOWER      | ceramic capacitor from CPH to CPL.                                                                                                                |

| VREF   | 33     | 34    | Input      | Voltage reference input for setting current regulation threshold.<br>DVDD can be used to provide VREF through a resistor divider.                 |

| DVDD   | 24     | 43    | Power      | Internal LDO output. Connect a X7R, 0.47- $\mu$ F to 1- $\mu$ F, 6.3-V or 10- V rated ceramic capacitor to GND.                                   |

| VCC    | 25     | 42    | Power      | Supply voltage for internal logic blocks. When separate logic supply voltage is not available, tie the VCC pin to the DVDD pin.                   |

| nFAULT | 26     | 41    | Open Drain | Fault indication output. Pulled logic low with fault condition. Open drain output requires an external pullup resistor.                           |

| MODE   | 28     | 39    | Input      | This pin programs the output rise/fall time.                                                                                                      |

| ОСРМ   | 27     | 40    | Input      | Determines the fault recovery method. Depending on the OCPM voltage, fault recovery can be either latch-off or auto-retry type.                   |

| nSLEEP | 42     | 25    | Input      | Sleep mode input. Logic high to enable device; logic low to enter low-<br>power sleep mode. A narrow nSLEEP reset pulse clears latched<br>faults. |

| PAD    | -      | -     | -          | Thermal pad.                                                                                                                                      |

# 6 Specifications 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted).

|                                                | MIN      | MAX                    | UNIT |

|------------------------------------------------|----------|------------------------|------|

| Power supply voltage (VM)                      | - 0.3    | 70                     | V    |

| Charge pump voltage (VCP, CPH)                 | - 0.3    | V <sub>VM</sub> + 5.75 | V    |

| Charge pump negative switching pin (CPL)       | - 0.3    | V <sub>VM</sub>        | V    |

| nSLEEP pin voltage (nSLEEP)                    | - 0.3    | V <sub>VM</sub>        | V    |

| Internal regulator voltage (DVDD)              | - 0.3    | 5.75                   | V    |

| External logic supply (VCC)                    | -0.3     | 5.75                   | V    |

| IPROPI pin voltage (IPROPI)                    | -0.3     | DVDD + 0.3             | V    |

| Control pin voltage                            | - 0.3    | 5.75                   | V    |

| Open drain output current (nFAULT)             | 0        | 10                     | mA   |

| Reference input pin voltage (VREF)             | - 0.3    | 5.75                   | V    |

| PGNDx to GND voltage                           | -0.5     | 0.5                    | V    |

| PGNDx to GND voltage, < 1 μs                   | -2.5     | 2.5                    | V    |

| Continuous OUTx pin voltage                    | - 1      | V <sub>VM</sub> + 1    | V    |

| Transient 100 ns OUTx pin voltage              | - 3      | V <sub>VM</sub> + 3    | V    |

| Peak drive current                             | Internal | ly Limited             | А    |

| Operating ambient temperature, T <sub>A</sub>  | - 40     | 125                    | °C   |

| Operating junction temperature, T <sub>J</sub> | - 40     | 150                    | °C   |

| Storage temperature, T <sub>stg</sub>          | - 65     | 150                    | °C   |

- Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- All voltage values are with respect to network ground terminal GND.

# 6.2 ESD Ratings

|                    |                            |                                                                       |             | VALUE | UNIT |

|--------------------|----------------------------|-----------------------------------------------------------------------|-------------|-------|------|

|                    |                            | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     |             | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | Corner pins | ±750  | V    |

|                    | aleenaige                  |                                                                       | Other pins  | ±500  |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                                | MIN  | MAX | UNIT |

|------------------|------------------------------------------------|------|-----|------|

| V <sub>VM</sub>  | Supply voltage range for normal (DC) operation | 4.5  | 65  | V    |

| VI               | Logic level input voltage                      | 0    | 5.5 | V    |

| V <sub>VCC</sub> | VCC pin voltage                                | 3.05 | 5.5 | V    |

| V <sub>REF</sub> | Reference voltage (VREF)                       | 0.05 | 3.3 | V    |

| f <sub>PWM</sub> | Applied PWM signal                             | 0    | 200 | kHz  |

### over operating free-air temperature range (unless otherwise noted)

|                  |                                 | MIN  | MAX | UNIT |

|------------------|---------------------------------|------|-----|------|

| I <sub>DDW</sub> | Current per output, DDW Package | 0    | 5   | A    |

| I <sub>DDV</sub> | Current per output, DDV Package | 0    | 10  | А    |

| T <sub>A</sub>   | Operating ambient temperature   | - 40 | 125 | °C   |

| TJ               | Operating junction temperature  | - 40 | 150 | °C   |

# 6.4 Thermal Information

|                        | THERMAL METRIC                               | DDW  | DDV  | UNIT |

|------------------------|----------------------------------------------|------|------|------|

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 22.2 | 44.2 | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 9.1  | 0.7  | °C/W |

| R <sub>0 JB</sub>      | Junction-to-board thermal resistance         | 5.3  | 18.9 | °C/W |

| ΨJT                    | Junction-to-top characterization parameter   | 0.1  | 0.3  | °C/W |

| ∲JB                    | Junction-to-board characterization parameter | 5.3  | 18.6 | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 0.7  | N/A  | °C/W |

### **6.5 Electrical Characteristics**

Typical values are at  $T_A = 25^{\circ}$ C and  $V_{VM} = 24$  V. All limits are over recommended operating conditions, unless otherwise noted.

|                      | PARAMETER                         | TEST CONDITIONS                                                               | MIN         | ТҮР                 | MAX  | UNIT       |

|----------------------|-----------------------------------|-------------------------------------------------------------------------------|-------------|---------------------|------|------------|

| OWER S               | UPPLIES (VM, DVDD)                |                                                                               |             |                     |      |            |

| VM                   | VM operating supply current       | nSLEEP = 1, No load, VCC = External<br>5V                                     |             | 4                   | 7    | mA         |

|                      |                                   | nSLEEP = 1, No load, VCC = DVDD                                               |             | 6                   | 9    |            |

| VMQ                  | VM sleep mode supply current      | nSLEEP = 0                                                                    |             | 3                   | 8    | μA         |

| SLEEP                | Sleep time                        | nSLEEP = 0 to sleep-mode                                                      | 120         |                     |      | μ <b>s</b> |

| RESET                | nSLEEP reset pulse                | nSLEEP low to clear fault                                                     | 20          |                     | 40   | μs         |

| WAKE                 | Wake-up time                      | nSLEEP = 1 to output transition                                               |             | 0.8                 | 1.2  | ms         |

| ON                   | Turn-on time                      | VM > UVLO to output transition                                                |             | 0.8                 | 1.3  | ms         |

| / <sub>DVDD</sub>    | Internal regulator voltage        | No external load, $6 V < V_{VM} < 65 V$<br>No external load, $V_{VM} = 4.5 V$ | 4.75<br>4.2 | 5<br>4.35           | 5.25 | V<br>V     |

| HARGE I              | PUMP (VCP, CPH, CPL)              |                                                                               |             |                     |      |            |

| / <sub>VCP</sub>     | VCP operating voltage             | 6 V < V <sub>VM</sub> < 65 V                                                  |             | V <sub>VM</sub> + 5 |      | V          |

| (VCP)                | Charge pump switching frequency   | V <sub>VM</sub> > UVLO; nSLEEP = 1                                            |             | 360                 |      | kHz        |

| OGIC-LE              | VEL INPUTS (IN1, IN2, IN3, IN4, E | N1, EN2, EN3, EN4, MODE, OCPM, nSLE                                           | EP)         |                     |      |            |

| / <sub>IL</sub>      | Input logic-low voltage           |                                                                               | 0           |                     | 0.6  | V          |

| / <sub>IH</sub>      | Input logic-high voltage          |                                                                               | 1.5         |                     | 5.5  | V          |

| / <sub>HYS</sub>     | Input logic hysteresis            |                                                                               |             | 150                 |      | mV         |

| L                    | Input logic-low current           | V <sub>IN</sub> = 0 V                                                         | - 1         |                     | 1    | μA         |

| н                    | Input logic-high current          | V <sub>IN</sub> = DVDD                                                        |             |                     | 50   | μA         |

| 1                    | ENx high to OUTx high delay       | INx = 1                                                                       |             |                     | 2    | μ <b>s</b> |

| 2                    | ENx low to OUTx low delay         | INx = 1                                                                       |             |                     | 2    | μs         |

| 3                    | ENx high to OUTx low delay        | INx = 0                                                                       |             |                     | 2    | μ <b>s</b> |

| 4                    | ENx low to OUTx high delay        | INx = 0                                                                       |             |                     | 2    | μ <b>s</b> |

| 5                    | INx high to OUTx high delay       |                                                                               |             | 600                 |      | ns         |

| 6                    | INx low to OUTx low delay         |                                                                               |             | 600                 |      | ns         |

| CONTROL              | OUTPUTS (nFAULT)                  | · · · · ·                                                                     | <b>I</b>    | 1                   | I    |            |

| / <sub>OL</sub>      | Output logic-low voltage          | I <sub>O</sub> = 5 mA                                                         |             |                     | 0.5  | V          |

| он                   | Output logic-high leakage         |                                                                               | - 1         |                     | 1    | μA         |

| NOTOR D              | RIVER OUTPUTS (OUT1, OUT2, O      | OUT3, OUT4)                                                                   |             |                     |      |            |

|                      |                                   | T <sub>J</sub> = 25 °C, I <sub>O</sub> = -5 A                                 |             | 50                  | 60   | mΩ         |

| R <sub>DS(ONH)</sub> | High-side FET on resistance       | T <sub>J</sub> = 125 °C, I <sub>O</sub> = -5 A                                |             | 75                  | 90   | mΩ         |

|                      |                                   | T <sub>J</sub> = 150 °C, I <sub>O</sub> = -5 A                                |             | 85                  | 105  | mΩ         |

|                      |                                   | T <sub>J</sub> = 25 °C, I <sub>O</sub> = 5 A                                  |             | 50                  | 60   | mΩ         |

| RDS(ONL)             | Low-side FET on resistance        | T <sub>J</sub> = 125 °C, I <sub>O</sub> = 5 A                                 |             | 75                  | 90   | mΩ         |

|                      |                                   | T <sub>J</sub> = 150 °C, I <sub>O</sub> = 5 A                                 |             | 85                  | 105  | mΩ         |

|                      |                                   | I <sub>O</sub> = 5 A, MODE = 1, between 10% and 90%                           |             | 70                  |      | ns         |

| RF                   | Output rise/fall time             | I <sub>O</sub> = 5 A, MODE = 0, between 10% and 90%                           |             | 140                 |      | ns         |

### TEXAS INSTRUMENTS www.ti.com.cn

Typical values are at  $T_A = 25^{\circ}$ C and  $V_{VM} = 24$  V. All limits are over recommended operating conditions, unless otherwise noted.

|                       | PARAMETER                        | TEST CONDITIONS                         | MIN  | TYP                 | MAX  | UNIT         |  |

|-----------------------|----------------------------------|-----------------------------------------|------|---------------------|------|--------------|--|

| t <sub>D</sub>        | Output dead time                 | VM = 24V, I <sub>O</sub> = 5 A          |      | 300                 |      | ns           |  |

| CURRENT               | SENSE AND REGULATION (IPRO       | PI, VREF)                               |      | I                   | I    |              |  |

| A <sub>IPROPI</sub>   | Current mirror gain              |                                         |      | 212                 |      | μ <b>Α/Α</b> |  |

|                       |                                  | 10% to 20% rated current                | -8.5 |                     | 8.5  | %            |  |

| A <sub>ERR</sub>      | Current mirror scaling error     | 20% to 40% rated current                | -5   |                     | 5    |              |  |

|                       |                                  | 40% to 100% rated current               | -4   |                     | 4    |              |  |

| I <sub>VREF</sub>     | VREF Leakage Current             | VREF = 3.3 V                            |      |                     | 100  | nA           |  |

| t <sub>OFF</sub>      | PWM off-time                     |                                         |      | 16                  |      | μ <b>S</b>   |  |

| t <sub>DEG</sub>      | Current regulation deglitch time |                                         |      | 0.5                 |      | μ <b>S</b>   |  |

| t <sub>BLK</sub>      | Current Regulation Blanking time |                                         |      | 1.5                 |      | μ <b>s</b>   |  |

| PROTECTI              | ON CIRCUITS                      | 1                                       |      | I                   | I    |              |  |

| V <sub>UVLO</sub>     | VM UVLO lockout                  | VM falling                              | 4.1  | 4.25                | 4.35 | V            |  |

| ♥ UVLO                |                                  | VM rising                               | 4.2  | 4.35                | 4.45 |              |  |

| VCC <sub>UVLO</sub>   | VCC UVLO lockout                 | VCC falling                             | 2.7  | 2.8                 | 2.9  | - V          |  |

| VCCUVLO               |                                  | VCC rising                              | 2.8  | 2.9                 | 3.05 |              |  |

| V <sub>UVLO,HYS</sub> | Undervoltage hysteresis          | Rising to falling threshold             |      | 100                 |      | mV           |  |

| V <sub>CPUV</sub>     | Charge pump undervoltage         | VCP falling                             |      | V <sub>VM</sub> + 2 |      | V            |  |

| 1                     |                                  | Current through any FET, DDW<br>Package | 8    |                     |      | А            |  |

| I <sub>OCP</sub>      | Overcurrent protection           | Current through any FET, DDV 16         |      |                     | А    |              |  |

| t <sub>OCP</sub>      | Overcurrent detection delay      |                                         |      | 2                   |      | μ <b>S</b>   |  |

| t <sub>RETRY</sub>    | Overcurrent retry time           |                                         |      | 4                   |      | ms           |  |

| T <sub>OTSD</sub>     | Thermal shutdown                 | Die temperature T <sub>J</sub>          | 150  | 165                 | 180  | °C           |  |

| T <sub>HYS_OTSD</sub> | Thermal shutdown hysteresis      | Die temperature T <sub>J</sub>          |      | 20                  |      | °C           |  |

**ADVANCE INFORMATION**

9

# 7 Detailed Description

# 7.1 Overview

The DRV8962 is a four-channel half-bridge driver that operates from 4.5 V to 65 V and supports a wide range of load currents for various types of loads. The device integrates four half-bridge output power stages. The device integrates a charge pump regulator to support efficient high-side N-channel MOSFETs and 100% duty cycle operation. The DRV8962 can operate from a single power supply input (VM). Alternatively, the VCC pin can be connected to a second power supply to provide power to the internal logic blocks. The nSLEEP pin provides an ultra-low power mode to minimize current draw during system inactivity.

The device is available in two packages - a 44-pin HTSSOP (DDW) package with exposed pad at the bottom of the package; and another 44-pin HTSSOP (DDV) package with exposed pad on the top of the package. The DDW package provides up to 5-A current per output. When used with a low thermal resistance heat sink installed on the top of the DDV package, the DRV8962 can deliver up to 10-A per output. The DRV8962 DDW package is pin-to-pin compatible with the DRV8952, which is rated for 48 V maximum operating voltage. The actual current that can be delivered depends on the ambient temperature, supply voltage, and PCB thermal design.

The DRV8962 provides current sense outputs. The IPROPI pins source a small current that is proportional to the current in the high-side MOSFETs. The current from the IPROPI pins can be converted to a proportional voltage using an external resistor ( $R_{IPROPI}$ ). The integrated current sensing allows the DRV8962 to limit the output current with a fixed off-time PWM chopping scheme and provide load information to the external controller to detect changes in load. The sense accuracy of the IPROPI output is ± 4% for 40% to 100% of rated current. External power sense resistors can also be connected if higher accuracy sensing is required. The current regulation level can be configured during operation through the VREF pin to limit the load current according to the system demands.

A variety of integrated protection features protect the device in the case of a system fault. These include undervoltage lockout (UVLO), charge pump undervoltage (CPUV), over current protection (OCP), and over temperature shutdown (OTSD). Fault conditions are indicated on the nFAULT pin.

**ADVANCE INFORMATION**

### 7.2 Functional Block Diagram

# 7.3 Feature Description

The following table shows the recommended values of the external components for the DRV8962.

### 表 7-1. External Components

| COMPONENT            | PIN 1       | PIN 2  | RECOMMENDED                                        |

|----------------------|-------------|--------|----------------------------------------------------|

| C <sub>VM1</sub>     | VM          | PGND1  | X7R, 0.01-µF, VM-rated ceramic capacitor           |

| C <sub>VM2</sub>     | VM          | PGND3  | X7R, 0.01-µF, VM-rated ceramic capacitor           |

| C <sub>VM3</sub>     | VM          | PGND1  | Bulk, VM-rated capacitor                           |

| C <sub>VCP</sub>     | VCP         | VM     | X7R, 1-μF, 16-V ceramic capacitor                  |

| C <sub>SW</sub>      | СРН         |        | X7R, 0.1-µF, VM-rated ceramic capacitor            |

| C <sub>DVDD</sub>    | DVDD        | GND    | X7R, 1-µF, 6.3-V or 10-V rated ceramic capacitor   |

| C <sub>VCC</sub>     | VCC         | GND    | X7R, 0.1-µF, 6.3-V or 10-V rated ceramic capacitor |

| R <sub>nFAULT</sub>  | DVDD or VCC | nFAULT | 10-kΩ resistor                                     |

| R <sub>REF1</sub>    | VREF        | DVDD   | Resistors to set current regulation threshold.     |

| R <sub>REF2</sub>    | VREF        | GND    |                                                    |

| R <sub>IPROPIx</sub> | IPROPIx     | GND    | For details, see 节 7.5.3                           |

# 7.4 Independent Half-bridge Operation

- The DRV8962 can drive four half-bridge loads simultaneously.

- The MODE pin configures the typical output rise and fall times to 70 ns or 140 ns.

- The ENx pins enable or disable (Hi-Z) the outputs.

- The INx pins control the state (high or low) of the outputs

- The INx pins can accept static or pulse-width modulated (PWM) signals.

- The INx and ENx inputs can be powered before VM is applied.

- The truth table does not take into account the internal current regulation feature.

- The device automatically handles the dead time generation when switching between the high-side and lowside MOSFET of a half-bridge.

|   |   | ENx                                          | OUTx | DESCRIPTION                        |  |  |  |  |  |

|---|---|----------------------------------------------|------|------------------------------------|--|--|--|--|--|

|   |   | Sleep mode, all half-bridges disabled (Hi-Z) |      |                                    |  |  |  |  |  |

| 1 | Х | 0                                            | Hi-Z | Individual outputs disabled (Hi-Z) |  |  |  |  |  |

| 1 | 0 | 1                                            | L    | OUTx Low-side ON                   |  |  |  |  |  |

| 1 | 1 | 1                                            | Н    | OUTx High-side ON                  |  |  |  |  |  |

#### 表 7-2. Independent Half-Bridge Operation Truth Table

The inputs can also be used for PWM control of, for example, the speed of a DC motor. When controlling a winding with PWM, when the drive current is interrupted, the inductive nature of the motor requires that the current must continue to flow. This is called recirculation current. To handle this recirculation current, the H-bridge can operate in two different states, fast decay or slow decay. In fast decay mode, the H-bridge is disabled and recirculation current flows through the body diodes; in slow decay, the motor winding is shorted.

To PWM using fast decay, the PWM signal is applied to the ENx pin; to use slow decay, the PWM signal is applied to the INx pin. The following table is an example of driving a DC motor using OUT1 and OUT2 as an H-bridge:

|  | IN1 | IN1         EN1         IN2         EN2           1         1         PWM         1 |   | FUNCTION |                         |  |

|--|-----|-------------------------------------------------------------------------------------|---|----------|-------------------------|--|

|  | 1   |                                                                                     |   | 1        | Forward PWM, slow decay |  |

|  | PWM | 1                                                                                   | 1 | 1        | Reverse PWM, slow decay |  |

|  | 1   | 1 PWM                                                                               |   | PWM      | Forward PWM, fast decay |  |

#### 表 7-3. PWM Function

#### 表 7-3. PWM Function (continued)

| IN1 | EN1 | IN2 | EN2 | FUNCTION                |  |

|-----|-----|-----|-----|-------------------------|--|

| 0   | PWM | 1   | PWM | Reverse PWM, fast decay |  |

### 7.5 Current Sensing and Regulation

The DRV8962 integrates current sensing across the high-side MOSFETs, current regulation, and current sense feedback. These features allow the device to sense the load current when the load is connected between output nodes and ground, without connecting an external sense resistor or sense circuitry; reducing system size, cost, and complexity. The current sense proportional outputs (IPROPI) allow the device to give detailed feedback to the controller about the load current.

### 7.5.1 Current Sensing and Feedback

$I_{PROPI} = I_{HS} \times A_{IPROPI}$

The DRV8962 supports four IPROPI outputs, one for each half-bridge. The IPROPI outputs represent the current of each high-side MOSFET, as shown below -

(1)

Where I<sub>HS</sub> is the current flowing through the high-side MOSFET and A<sub>IPROPI</sub> is the current mirror gain.

Each IPROPI pin should be connected to an external resistor ( $R_{IPROPI}$ ) to ground in order to generate a proportional voltage ( $V_{IPROPI}$ ) on the IPROPI pin. This allows the current to be measured as the voltage drop across the  $R_{IPROPI}$  resistor with a standard analog to digital converter (ADC). The  $R_{IPROPI}$  resistor can be sized based on the expected load current in the application so that the full range of the controller ADC is utilized. The device implements an internal clamp circuit to limit  $V_{IPROPI}$  with respect to  $V_{VREF}$  on the VREF pin and protect the external ADC in case of output overcurrent or unexpected high current events. The IPROPI voltage should be less than the maximum recommended value of VREF, which is 3.3V.

The corresponding IPROPI voltage to the output current can be calculated as shown below -

#### 图 7-1. Integrated Current Sensing

The  $A_{ERR}$  parameter in the Electrical Characteristics table is the error associated with the  $A_{IPROPI}$  gain. It indicates the combined effect of offset error added to the  $I_{OUT}$  current and gain error.

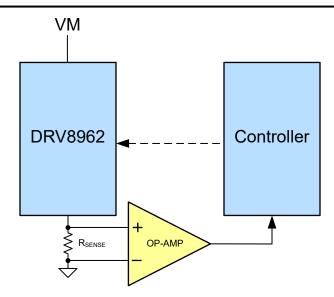

### 7.5.2 Current Sensing with External Resistor

The IPROPI output accuracy is  $\pm 4\%$  for 40% to 100% of rated current. If more accurate current sensing is desired, external sense resistors can also be used between the PGND pins and the system ground to sense the load currents, as shown below.

Copyright © 2022 Texas Instruments Incorporated

**ADVANCE INFORMATION**

(3)

### 图 7-2. Current Sensing with External Resistor

The voltage drop across the external sense resistor should not exceed 300 mV.

Place the sense resistors as close as possible to the corresponding IC pins. Use a symmetrical sense resistor layout to ensure good matching. Low-inductance sense resistors should be used to prevent voltage spikes and ringing. For optimal performance, the sense resistor should be a surface-mount resistor rated for high enough power.

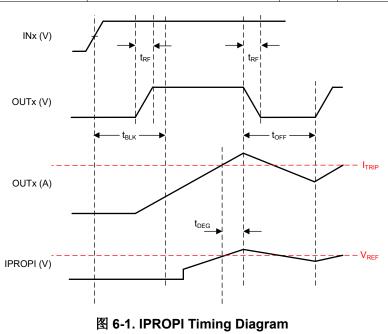

### 7.5.3 Current Regulation

The current chopping threshold ( $I_{TRIP}$ ) is set through a combination of the VREF voltage ( $V_{VREF}$ ) and IPROPI output resistor ( $R_{IPROPI}$ ). This is done by comparing the voltage drop across the external  $R_{IPROPI}$  resistor to  $V_{VREF}$  with an internal comparator.

$$I_{\text{TRIP}} \times A_{\text{IPROPI}} = V_{\text{VREF}} (V) / R_{\text{IPROPI}} (\Omega)$$

For example, to set  $I_{TRIP}$  at 5 A with  $V_{VREF}$  at 3.3 V,  $R_{IPROPI}$  has to be -

$R_{IPROPI} = V_{VREF} / (I_{TRIP} x A_{IPROPI}) = 3.3 / (5 x 212 x 10^{-6}) = 3.09 k\Omega$

The internal current regulation can be disabled by tying IPROPI to GND and setting the VREF pin voltage greater than GND (if current feedback is not required). If current feedback is required and current regulation is not required, set  $V_{VREF}$  and  $R_{IPROPI}$  such that  $V_{IPROPI}$  never reaches the  $V_{VREF}$  threshold.

The DRV8962 can simultaneously drive up to four resistive or inductive loads. When an output load is connected to ground, the load current can be regulated to the  $I_{TRIP}$  level. The PWM off-time ( $t_{OFF}$ ) is fixed at 16  $\mu$  s. The fixed off-time mode allows for a simple current chopping scheme without involvement from the external controller. Fixed off-time mode will support 100% duty cycle current regulation.

Another way of controlling the load current is the cycle-by-cycle control mode, where PWM pulse width of the INx input pins have to be controlled. This allows for additional control of the current chopping scheme by the external controller.

Few scenarios of driving high-side and low-side loads are described below -

#### Resistive loads connected to ground:

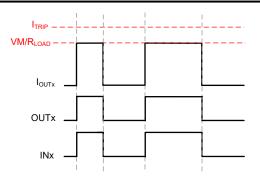

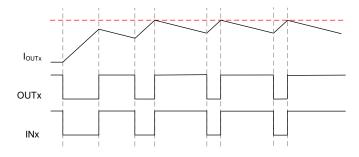

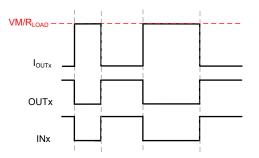

The regulated current will not exceed  $I_{TRIP}$ . If  $I_{TRIP}$  is higher than the (VM /  $R_{LOAD}$ ), the load current is regulated at VM /  $R_{LOAD}$  level while INx = 1 (shown in [8] 7-3).

### 图 7-3. Resistive Load Connected to ground, Cycle-by-cycle control

### Inductive loads connected to ground:

It should be ensured that the current decays enough every cycle to prevent runaway and triggering overcurrent protection.

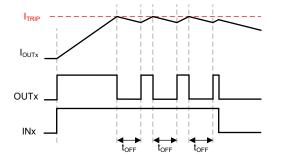

• For the scenario shown in  $\boxtimes$  7-4, with INx = 1, the low-side MOSFET is turned on for t<sub>OFF</sub> duration after I<sub>OUT</sub> exceeds I<sub>TRIP</sub>. After t<sub>OFF</sub>, the high side MOSFET is again turned on till I<sub>OUT</sub> exceeds I<sub>TRIP</sub> again.

图 7-4. Inductive Load Connected to ground, fixed off-time current chopping

If, after the  $t_{OFF}$  time has elapsed the current is still higher than the  $I_{TRIP}$  level, the device enforces another  $t_{OFF}$  time period of the same duration. The OFF time extension will continue till sensed current is less than  $I_{TRIP}$  at the end of  $t_{OFF}$  time.

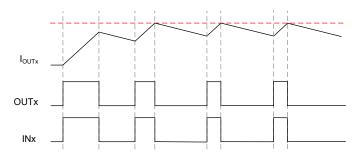

• Loads can also be controlled using the cycle-by-cycle method. When INx = 1, the current through the load builds up; and when INx = 0, the current through the load decays. By properly choosing the duty cycle of the INx pulse, current can be regulated to a target value. Various such scenarios are shown in 图 7-5 and 图 7-6.

图 7-5. Inductive Load Connected to ground, Cycle-by-cycle control

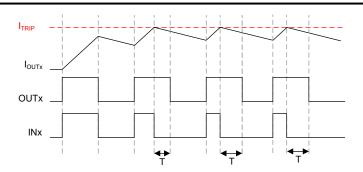

The next scenario requires INx pin duty cycle adjustment (T has to be less than  $T_{OFF}$ ) to ensure that the current does not run away.

图 7-6. Inductive Load Connected to ground, Cycle-by-cycle control

### Loads connected to VM:

Such loads can be controlled by controlling the INx pin pulse width: INx = 0 builds up the current, and INx = 1 decays the current, as shown in  $\mathbb{E}$  7-7 and  $\mathbb{E}$  7-8.

图 7-7. Inductive Load Connected to VM, Cycle-by-cycle control

This scenario requires INx pin duty cycle adjustment to ensure that the current does not run away.

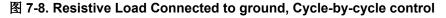

### 7.6 Charge Pump

A charge pump is integrated to supply the high-side N-channel MOSFET gate-drive voltage. The charge pump requires a capacitor between the VM and VCP pins to act as the storage capacitor. Additionally a ceramic capacitor is required between the CPH and CPL pins to act as the flying capacitor.

图 7-9. Charge Pump Block Diagram

# 7.7 Linear Voltage Regulator

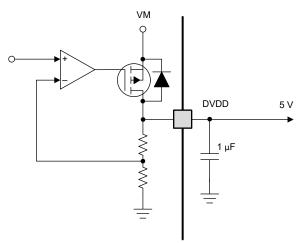

A linear voltage regulator is integrated in the device. When the VCC pin is connected to DVDD, the DVDD regulator provides power to the low-side gate driver and all the internal circuits. For proper operation, bypass the DVDD pin to GND using a 1  $\mu$  F ceramic capacitor. The DVDD output is nominally 5-V.

图 7-10. Linear Voltage Regulator Block Diagram

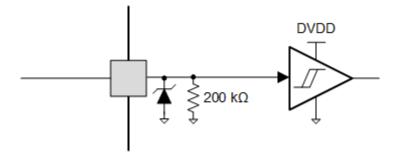

If a digital input must be tied permanently high, tying the input to the DVDD pin instead of an external regulator is preferred. This method saves power when the VM pin is not applied or in sleep mode: the DVDD regulator is disabled and current does not flow through the input pulldown resistors. For reference, logic level inputs have a typical pulldown of 200 k $\Omega$ .

The nSLEEP pin cannot be tied to DVDD, else the device will never exit sleep mode.

# 7.8 VCC Voltage Supply

An external voltage can be applied to the VCC pin to power the internal logic circuitry. The voltage on the VCC pin should be between 3.05 V and 5.5 V and should be well regulated. When an external supply is not available, VCC must be connected to the DVDD pin of the device.

When powered by the VCC, the internal logic blocks do not consume power from the VM supply rail - thereby reducing the power loss in the DRV8962. This is beneficial in high voltage applications, and when ambient temperature is high. Bypass the VCC pin to ground using a 0.1  $\mu$  F ceramic capacitor.

# 7.9 Logic Level Pin Diagram

The pin diagram below shows the input structure for INx, ENx, MODE, OCPM and nSLEEP pins.

图 7-11. Logic-Level Input Pin Diagram

# 7.10 Protection Circuits

The device is fully protected against supply undervoltage, charge pump undervoltage, output overcurrent, and device overtemperature events.

### 7.10.1 VM Undervoltage Lockout (UVLO)

If at any time the voltage on the VM pin falls below the UVLO threshold voltage:

- All the outputs are disabled (High-Z)

- nFAULT pin is driven low

- The charge pump is disabled

Normal operation resumes (driver operation and nFAULT released) when the VM voltage recovers above the UVLO rising threshold voltage.

# 7.10.2 VCP Undervoltage Lockout (CPUV)

If at any time the voltage on the VCP pin falls below the CPUV voltage:

- All the outputs are disabled (High-Z)

- nFAULT pin is driven low

- The charge pump remains active

Normal operation resumes (driver operation and nFAULT released) when the VCP undervoltage condition is removed.

# 7.10.3 Logic Supply Power on Reset (POR)

If at any time the voltage on the VCC pin falls below the  $VCC_{UVLO}$  threshold:

- All the outputs are disabled (High-Z)

- Charge pump is disabled

VCC UVLO is not reported on the nFAULT pin. Normal motor-driver operation resumes when the VCC undervoltage condition is removed.

# 7.10.4 Overcurrent Protection (OCP)

Analog current-limit circuit on each MOSFET limits the current through that MOSFET by removing the gate drive. If this current limit persists for longer than the t<sub>OCP</sub> time, an overcurrent fault is detected.

• Only the half-bridge experiencing the overcurrent will be disabled

- nFAULT is driven low

- Charge pump remains active

Overcurrent conditions on both high and low side MOSFETs; meaning a short to ground or short to supply will result in an overcurrent fault detection.

Once the overcurrent condition is removed, the recovery mechanism depends on the OCPM pin setting. OCPM pin programs either latch-off or automatic retry type recovery.

- When the OCPM pin is logic low, the device has latch-off type recovery which means once the OCP condition is removed, normal operation resumes after applying an nSLEEP reset pulse or a power cycling.

- When the OCPM pin is logic high, normal operation resumes automatically (driver operation and nFAULT released) after the t<sub>RETRY</sub> time has elapsed and the fault condition is removed.

### 7.10.5 Thermal Shutdown (OTSD)

Thermal shutdown is detected if the die temperature exceeds the thermal shutdown limit ( $T_{OTSD}$ ). When thermal shutdown is detected -

- · All MOSFETs in the Half-bridges are disabled

- nFAULT is driven low

- Charge pump is disabled

Once the thermal shutdown condition is removed, the recovery mechanism depends on the OCPM pin setting. OCPM pin programs either latch-off or automatic retry type recovery.

- When the OCPM pin is logic low, the device has latch-off type recovery which means after the junction temperature falls below the overtemperature threshold limit minus the hysteresis (T<sub>OTSD</sub> - T<sub>HYS\_OTSD</sub>), normal operation resumes after applying an nSLEEP reset pulse or a power cycling.

- When the OCPM pin is logic high, normal operation resumes automatically after the junction temperature falls below the overtemperature threshold limit minus the hysteresis (T<sub>OTSD</sub> - T<sub>HYS OTSD</sub>).

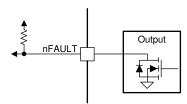

### 7.10.6 nFAULT Output

The nFAULT pin has an open-drain output and should be pulled up to a 5-V, 3.3-V or 1.8-V supply. When a fault is detected, the nFAULT pin will be logic low. nFAULT pin will be high after power-up. For a 5-V pullup, the nFAULT pin can be tied to the DVDD pin with a resistor. For a 3.3-V or 1.8-V pullup, an external supply must be used.

图 7-12. nFAULT Pin

#### 7.10.7 Fault Condition Summary

| FAULT                      | CONDITION                 | ERROR<br>REPORT | Half-BRIDGE | CHARGE<br>PUMP | LOGIC     | RECOVERY                  |

|----------------------------|---------------------------|-----------------|-------------|----------------|-----------|---------------------------|

| VM undervoltage<br>(UVLO)  | VM < V <sub>UVLO</sub>    | nFAULT          | Disabled    | Disabled       | Reset     | VM > V <sub>UVLO</sub>    |

| VCP undervoltage<br>(CPUV) | VCP < V <sub>CPUV</sub>   | nFAULT          | Disabled    | Operating      | Operating | VCP > V <sub>CPUV</sub>   |

| Logic Supply POR           | VCC < VCC <sub>UVLO</sub> | -               | Disabled    | Disabled       | Reset     | VCC > VCC <sub>UVLO</sub> |

| yer in tual contaition cummuly (contaition) |                                               |                 |             |                |           |                                                                          |  |  |

|---------------------------------------------|-----------------------------------------------|-----------------|-------------|----------------|-----------|--------------------------------------------------------------------------|--|--|

| FAULT                                       | CONDITION                                     | ERROR<br>REPORT | Half-BRIDGE | CHARGE<br>PUMP | LOGIC     | RECOVERY                                                                 |  |  |

| Overcurrent (OCP)                           | I <sub>OUT</sub> > I <sub>OCP,</sub> OCPM = 0 | nFAULT          | Disabled    | Operating      | Operating | Latched:<br>nSLEEP reset pulse                                           |  |  |

|                                             | I <sub>OUT</sub> > I <sub>OCP,</sub> OCPM = 1 | nFAULT          | Disabled    | Operating      | Operating | Automatic retry: t <sub>RETRY</sub>                                      |  |  |

| Thermal Shutdown                            | $T_J > T_{TSD}$ , OCPM = 0                    | nFAULT          | Disabled    | Disabled       | Operating | Latched:<br>nSLEEP reset pulse                                           |  |  |

| (OTSD)                                      | T <sub>J</sub> > T <sub>TSD,</sub> OCPM = 1   | nFAULT          | Disabled    | Disabled       | Operating | Automatic: T <sub>J</sub> < T <sub>OTSD</sub> -<br>T <sub>HYS_OTSD</sub> |  |  |

### 表 7-4. Fault Condition Summary (continued)

# 7.11 Device Functional Modes

### 7.11.1 Sleep Mode

When the nSLEEP pin is low, the device enters a low-power sleep mode. In sleep mode, all the internal MOSFETs, the DVDD regulator, SPI and the charge pump is disabled. The t<sub>SLEEP</sub> time must elapse after a falling edge on the nSLEEP pin before the device enters sleep mode. The device is brought out of sleep automatically if the nSLEEP pin is brought high. The t<sub>WAKE</sub> time must elapse before the device is ready for inputs.

### 7.11.2 Operating Mode

This mode is enabled when -

- nSLEEP is high

- VM > UVLO

The t<sub>WAKE</sub> time must elapse before the device is ready for inputs.

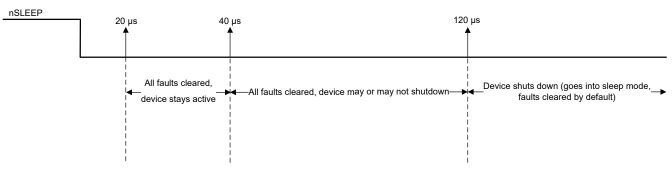

### 7.11.3 nSLEEP Reset Pulse

A latched fault can be cleared by an nSLEEP reset pulse. This pulse width must be greater than 20  $\mu$ s and smaller than 40  $\mu$ s. If nSLEEP is low for longer than 40  $\mu$ s, but less than 120  $\mu$ s, the faults are cleared and the device may or may not shutdown, as shown in the timing diagram below. This reset pulse does not affect the status of the charge pump or other functional blocks.

### 图 7-13. nSLEEP Reset Pulse

### 7.11.4 Functional Modes Summary

表 7-5 lists a summary of the functional modes.

| CONDITION  |                   | CONFIGURATI<br>ON | Half-BRIDGE | DVDD Regulator | CHARGE PUMP | Logic     |

|------------|-------------------|-------------------|-------------|----------------|-------------|-----------|

| Sleep mode | 4.5 V < VM < 65 V | nSLEEP pin = 0    | Disabled    | Disbaled       | Disabled    | Disabled  |

| Operating  | 4.5 V < VM < 65 V | nSLEEP pin = 1    | Operating   | Operating      | Operating   | Operating |

**ADVANCE INFORMATION**

# 8 Application and Implementation

### 备注

以下应用部分中的信息不属于 TI 器件规格的范围, TI 不担保其准确性和完整性。TI 的客 户应负责确定器件是否适用于其应用。客户应验证并测试其设计,以确保系统功能。

# 8.1 Application Information

The DRV8962 can be used to drive the following types of loads -

- · Up to four solenoid loads

- One stepper motor

- Two brushed-DC motors

- One 3-phase sinewave Brushless-DC motor

- One 3-phase Permanent magnet synchronous motor (PMSM)

- One or two thermoelectric coolers (TEC)

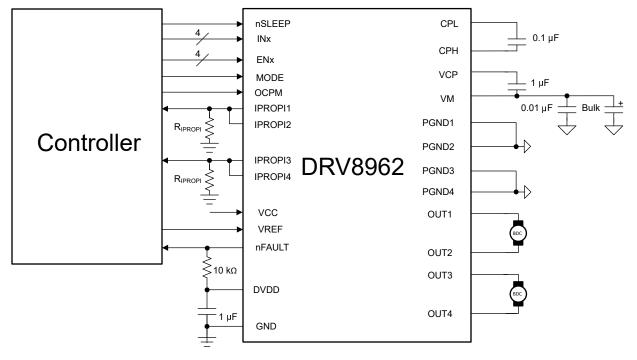

### 8.1.1 Driving Solenoid Loads

The DRV8962 can drive four solenoid loads at the same time. For loads connected to ground, the IPROPI pins output the load current information; and the load current can be regulated to an  $I_{TRIP}$  level determined by the voltage on the VREF pin.

The DRV8962 supports independent IN and EN pins for each of the four half-bridges. All the four half-bridges also have separate PGND pins.

### 8.1.1.1 Solenoid Driver Typical Application

图 8-1 shows a schematic of the DRV8962 driving four loads connected to ground.

图 8-1. Driving Solenoids with DRV8962

#### 8.1.1.2 Thermal Calculations

The output current and power dissipation capabilities of the device are heavily dependent on the PCB design and external system conditions. This section provides some guidelines for calculating these values.

Total power dissipation for the device is composed of three main components. These are the power MOSFET  $R_{DS(ON)}$  (conduction) losses, the power MOSFET switching losses and the quiescent supply current dissipation.

While other factors may contribute additional power losses, these other items are typically insignificant compared to the three main items.

### 8.1.1.2.1 Power Loss Calculations

The total power dissipation in each half-bridge can be calculated as -

$$P_{HB} = P_{HS} + P_{LS} = [R_{DS(ON)} \times I_{L}^{2}] + [((2 \times V_{D} \times t_{D}) + (VM \times t_{RF})) \times I_{L} \times f_{PWM}]$$

Where,

- R<sub>DS(ON)</sub> = ON resistance of each FET

- For DRV8962, it is typically 50 m  $\Omega$  at 25 °C, and 85 m  $\Omega$  at 150 °C.

- f<sub>PWM</sub> = PWM switching frequency

- VM = Supply voltage to the driver

- I<sub>L</sub> = Load current

- D = PWM duty cycle (between 0 and 1)

- t<sub>RF</sub> = Output voltage rise/ fall time

- For DRV8962, the rise/fall time is either 70 ns or 140 ns

- V<sub>D</sub> = FET body diode forward bias voltage

- For DRV8962, it is 1 V

- t<sub>D</sub> = dead time

- For DRV8962, it is 300 ns

So, total power dissipation in the DRV8962 is -

$P_{TOT} = n \times P_{HB} + P_Q$

Where n is the number of half-bridges switching at the same time, and  $P_Q$  is the quiescent power loss.

For this example, let us assume -

- · All four half-bridges are switching

- VM = 24 V

- I<sub>L</sub> = 4 A

- Ambient temperature (T<sub>A</sub>) = 25 °C

- t<sub>RF</sub> = 70 ns

- Input PWM frequency = 20 kHz

When the VCC pin is connected to an external power supply, the quiescent current is 4 mA, and therefore  $P_Q$  will be (24 V x 4 mA) = 96 mW.

$P_{HB} = [50 \text{ m} \Omega \times 4^{2}] + [((2 \text{ x } 1 \text{ V } \text{ x } 300 \text{ ns}) + (24 \text{ V } \text{ x } 70 \text{ ns})) \text{ x } 4 \text{ A } \text{ x } 20 \text{ KHz}] = 0.982 \text{ W}$

$P_{TOT} = (4 \times 0.982) + 0.096 = 4.024 W$

#### 8.1.1.2.2 Junction Temperature Estimation

The estimated junction temperature will be:  $T_J = T_A + (P_{TOT} x \theta_{JA})$

The junction-to-ambient thermal resistance  $\theta_{JA}$  is 22.2 °C/W for the DDW package on a JEDEC standard PCB, and close to 5 °C/W for the DDV package if a suitable heat sink is used.

Therfore, the first estimate of the junction temperature is -

$T_J = T_A + (P_{TOT} \times \theta_{JA}) = 25 + (4.024 \times 22.2) = 114.3 \text{°C}$

For more accurate calculation, consider the dependency of on-resistance of FETs with device junction temperature shown in the Typical Operating Characteristics section.

For example,

- At 114.3 °C junction temperature, the on-resistance will likely increase by a factor of 1.35 compared to the onresistance at 25 °C.

- The initial estimate of conduction loss (loss due to R<sub>DS(ON)</sub>) for each half-bridge was 0.8 W.

- New estimate of conduction loss will therefore be 0.8 W x 1.35 = 1.08 W.

- New estimate of the total power loss will accordingly be 5.144 W.

- New estimate of junction temperature for the DDW package will be 139.2 °C.

- · Further iterations are unlikely to increase the junction temperature estimate by significant amount.

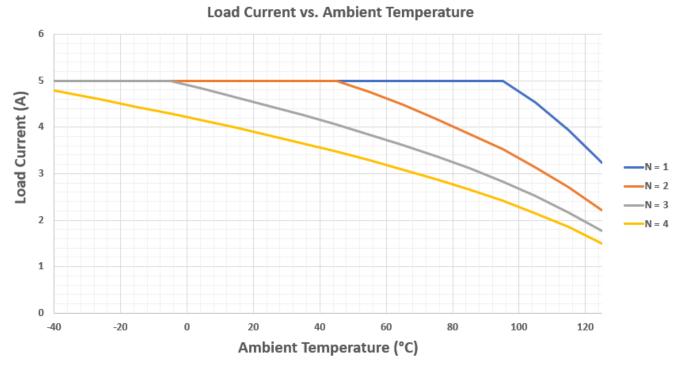

The following plot estimates the current that can be delivered from each output of the DDW package as a function of the ambient temperature and the number of half-bridges (N) switching at any time, with the following assumptions:

- VM = 24 V

- t<sub>RF</sub> = 70 ns

- f<sub>PWM</sub> = 20 kHz

- T<sub>1</sub> = 150 °C

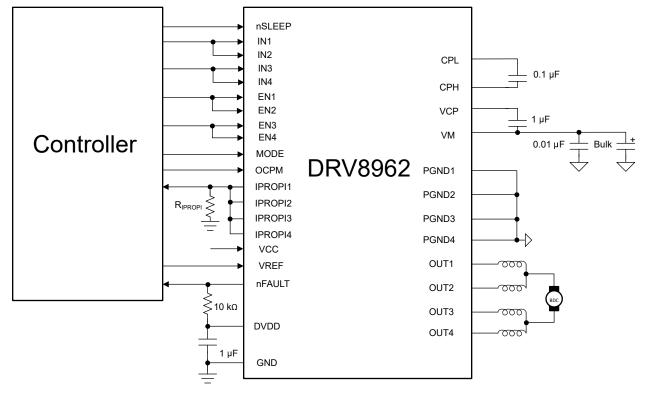

#### 8.1.2 Driving Stepper Motors

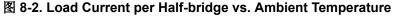

The DRV8962 can drive one stepper motor using the PWM input interface.

### 8.1.2.1 Stepper Driver Typical Application

The following schematic shows the DRV8962 driving a stepper motor.

#### 图 8-3. Driving Stepper Motor with DRV8962

The full-scale current ( $I_{FS}$ ) is the maximum current driven through either winding. This quantity will depend on the VREF voltage and the resistor connected from IPROPI pin to ground.

#### I<sub>FS</sub> x A<sub>IPROPI</sub> = V<sub>VREF</sub> / R<sub>IPROPI</sub>

The maximum allowable voltage on the VREF pins is 3.3 V. DVDD can be used to provide VREF through a resistor divider.

#### 备注

The I<sub>FS</sub> current must also follow  $\beta$ 程式 4 to avoid saturating the motor. VM is the motor supply voltage, and R<sub>L</sub> is the motor winding resistance.

$$I_{FS} (A) < \frac{VM(V)}{R_{L} (\Omega) + 2 \times R_{DS(ON)} (\Omega)}$$

If the target motor speed is too high, the motor will not spin. Make sure that the motor can support the target speed.

For a desired motor speed (v), microstepping level ( $n_m$ ), and motor full step angle ( $\theta_{step}$ ), determine the frequency of the input waveform as follows -

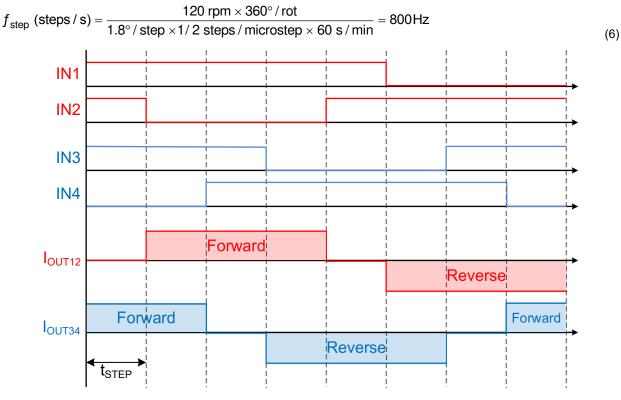

$$f_{\text{step}} (\text{steps / s}) = \frac{v (\text{rpm}) \times 360 (^{\circ}/\text{rot})}{\theta_{\text{step}} (^{\circ}/\text{step}) \times n_{\text{m}} (\text{steps / microstep}) \times 60 (\text{s}/\text{min})}$$

(5)

$\theta_{\mbox{ step}}$  can be found in the stepper motor data sheet or written on the motor itself.

The frequency  $f_{step}$  gives the frequency of input change on the DRV8962. 1/  $f_{step}$  =  $t_{STEP}$  on the diagram below.  $\overline{f}$ 程式 6 shows an example calculation for a 120 rpm target speed and 1/2 step.

(4)

图 8-4. Example 1/2 Stepping Operation

Connect the IPROPI outputs corresponding to the same H-bridge together. IPROPI1 and IPROPI2, when connected together, reprsent the current of coil A of the stepper (connected between OUT1 and OUT2) during drive and slow-decay (high-side recirculation) modes. Similarly, IPROPI3 and IPROPI4, connected together, will reprsent coil B current.

When two IPROPI pins are connected together, the effective current mirror gain will be 424  $\mu$  A/A typical. The resistor from the combined IPROPI pin to ground should be selected accordingly.

# 8.1.2.2 Power Loss Calculations

The following calculations assume a use case where the supply voltage is 24 V, full-scale current is 5 A, rise/fall time is 140 ns and input PWM frequency is 30-kHz.

The total power dissipation constitutes of three main components - conduction loss ( $P_{COND}$ ), switching loss ( $P_{SW}$ ) and power loss due to quiescent current consumption ( $P_Q$ ).

The conduction loss ( $P_{COND}$ ) depends on the motor rms current ( $I_{RMS}$ ) and high-side ( $R_{DS(ONH)}$ ) and low-side ( $R_{DS(ONL)}$ ) on-state resistances as shown in  $\overline{5}$ 程式 7.

$$P_{\text{COND}} = 2 \text{ x } (I_{\text{RMS}})^2 \text{ x } (R_{\text{DS(ONH)}} + R_{\text{DS(ONL)}})$$

The conduction loss for the typical application shown in 节 8.1.2.1 is calculated in 方程式 8.

$$P_{\text{COND}} = 2 \times (I_{\text{RMS}})^2 \times (R_{\text{DS(ONH)}} + R_{\text{DS(ONL)}}) = 2 \times (5 - A / \sqrt{2})^2 \times (0.1 - \Omega) = 2.5 - W$$

(8)

The power loss due to the PWM switching frequency depends on the output voltage rise/fall time ( $t_{RF}$ ), supply voltage, motor RMS current and the PWM switching frequency. The switching losses in each H-bridge during rise-time and fall-time are calculated as shown in  $\overline{5}$  Rt 9 and  $\overline{5}$  Rt 10.

$P_{SW_{RISE}} = 0.5 \text{ x } V_{VM} \text{ x } I_{RMS} \text{ x } t_{RF} \text{ x } f_{PWM}$

(7)

**ADVANCE INFORMATION**

# $P_{SW\_FALL} = 0.5 \text{ x } V_{VM} \text{ x } I_{RMS} \text{ x } t_{RF} \text{ x } f_{PWM}$

After substituting the values of various parameters, the switching losses in each H-bridge are calculated as shown below -

$$P_{SW_{RISE}} = 0.5 \times 24 \text{-V} \times (5\text{-A} / \sqrt{2}) \times (140 \text{ ns}) \times 30\text{-kHz} = 0.178\text{-W}$$

(11)

$$P_{SW_{FALL}} = 0.5 \times 24 \text{-V} \times (5\text{-A} / \sqrt{2}) \times (100 \text{ ns}) \times 30\text{-kHz} = 0.178\text{-W}$$

(12)

The total switching loss for the stepper motor driver (PSW) is calculated as twice the sum of rise-time (PSW RISE) switching loss and fall-time (P<sub>SW FALL</sub>) switching loss as shown below -

$$P_{SW} = 2 x (P_{SW RISE} + P_{SW FALL}) = 2 x (0.178 - W + 0.178 - W) = 0.712 - W$$

(13)

备注

The output rise/fall time (t<sub>RF</sub>) is expected to change based on the supply-voltage, temperature and device to device variation.

When the VCC pin is connected to an external voltage, the quiescent current is typically 4 mA. The power dissipation due to the quiescent current consumed by the power supply is calculated as shown below -

$$P_Q = V_{VM} \times I_{VM}$$

Substituting the values, quiescent power loss can be calculated as shown below -

$$P_Q = 24$$

-V x 4-mA = 0.096-W

The quiescent power loss is calculated using the typical operating supply current ( $I_{VM}$ ) which is dependent on supply-voltage, temperature and device to device variations.

备注

The total power dissipation (P<sub>TOT</sub>) is calculated as the sum of conduction loss, switching loss and the quiescent power loss as shown in 方程式 16.

$P_{TOT} = P_{COND} + P_{SW} + P_{Q} = 2.5 - W + 0.712 - W + 0.096 - W = 3.308 - W$ (16)

#### 8.1.2.3 Junction Temperature Estimation

For an ambient temperature of  $T_A$  and total power dissipation ( $P_{TOT}$ ), the junction temperature ( $T_J$ ) is calculated as -

$T_J = T_A + (P_{TOT} \times R_{\theta} J_A)$

Considering a JEDEC standard 4-layer PCB, the junction-to-ambient thermal resistance (R <sub>0.JA</sub>) is 22.2 °C/W for the DDW package.

Assuming 25°C ambient temperature, the junction temperature for the DDW package is calculated as shown below -

$$T_J = 25^{\circ}C + (3.308 - W \times 22.2 \ ^{\circ}C/W) = 98.4 \ ^{\circ}C$$

(17)

For more accurate calculation, consider the dependency of on-resistance of FETs with device junction temperature shown in the Typical Operating Characteristics section.

For example,

NSTRUMENTS

FXAS

(14)

(15)

(18)

- At 98.4 °C junction temperature, the on-resistance will likely increase by a factor of 1.25 compared to the onresistance at 25 °C.

- The initial estimate of conduction loss was 2.5 W.

- New estimate of conduction loss will therefore be 2.5 W x 1.25 = 3.125 W.

- New estimate of the total power loss will accordingly be 3.933 W.

- New estimate of junction temperature for the DDW package will be 112.3 °C.

- · Further iterations are unlikely to increase the junction temperature estimate by significant amount.

When using the DDV package, if a heat sink with less than 4 °C/W thermal resistance is chosen, the junction to ambient thermal resistance can be lower than 5 °C/W. The initial estimate of the junction temperature with the DDV package in this application will therefore be -

T<sub>J</sub> = 25°C + (3.308-W x 5 °C/W) = 41.5 °C

As the DDV package results in low thermal resistance, it can deliver 10 A full-scale current.

### 8.1.3 Driving Brushed-DC Motors

The DRV8962 can be used to drive one or two brushed-DC motors.

#### 8.1.3.1 Brushed-DC Driver Typical Application

The schematic below shows the DRV8962 driving two brushed-DC motors.

图 8-5. Driving two Brushed-DC Motors with DRV8962

The following truth table describes how to control brushed-DC motors -

表 8-1. Brushed-DC Motor Truth Table

| Function | EN1 | EN2 | IN1 | IN2 | OUT1 | OUT2 |

|----------|-----|-----|-----|-----|------|------|

| Forward  | 1   | 1   | 1   | PWM | н    | H/L  |

| Reverse  | 1   | 1   | PWM | 1   | H/L  | н    |

| Brake    | 1   | 1   | 1   | 1   | Н    | Н    |

| Brake*   | 1   | 1   | 0   | 0   | L    | L    |

表 8-1. Brushed-DC Motor Truth Table (continued)

| Coast* | 0 | X | Х | X | Z | х |

|--------|---|---|---|---|---|---|

| Coast* | х | 0 | х | Х | х | Z |

\* IPROPI pins will not output proportional current in these conditions.

### 8.1.3.2 Power Loss Calculation

For a H-bridge with high-side recirculation, power dissipation for each FET can be approximated as follows:

•  $P_{HS1} = R_{DS(ON)} \times I_{L}^{2}$

- P<sub>LS1</sub> = 0

- $P_{HS2} = [R_{DS(ON)} \times I_L^2 x (1-D)] + [2 x V_D x I_L x t_D x f_{PWM}]$

- $P_{LS2} = [R_{DS(ON)} \times I_L^2 \times D] + [VM \times I_L \times t_{RF} \times f_{PWM}]$

For estimating power dissipation for load current flow in the reverse direction, identical equations apply, with only swapping of HS1 with HS2 and LS1 with LS2.

Substituting the following values in the equations above -

- VM = 24 V

- I<sub>L</sub> = 4 A

- R<sub>DS(ON)</sub> = 50 m Ω

- D = 0.5

- V<sub>D</sub> = 1 V

- t<sub>D</sub> = 300 ns

- t<sub>RF</sub> = 70 ns

- f<sub>PWM</sub> = 20 kHz

The losses in each FET can be calculated as follows -

$P_{HS1} = 50 \text{ m} \Omega \times 4^2 = 0.8 \text{ W}$

$P_{LS1} = 0$

P<sub>HS2</sub> = [50 m Ω × 4<sup>2</sup> x (1-0.5)] + [2 x 1 V x 4 A x 300 ns x 20 KHz] = 0.448 W

$P_{LS2} = [50 \text{ m} \Omega \times 4^2 \text{ x} 0.5] + [24 \text{ x} 4 \text{ A} \text{ x} 70 \text{ ns} \text{ x} 20 \text{ kHz}] = 0.534 \text{ W}$

Quiescent Current Loss P<sub>Q</sub> = 24 V × 4 mA = 0.096 W

$P_{TOT} = 2 x (P_{HS1} + P_{LS1} + P_{HS2} + P_{LS2}) + P_Q = 2 x (0.8 + 0 + 0.448 + 0.534) + 0.096 = 3.66 W$

#### 8.1.3.3 Junction Temperature Estimation

For an ambient temperature of  $T_A$  and total power dissipation ( $P_{TOT}$ ), the junction temperature ( $T_J$ ) is calculated as -

$T_{J} = T_{A} + (P_{TOT} \times R_{\theta} J_{A})$

Considering a JEDEC standard 4-layer PCB, the junction-to-ambient thermal resistance (R  $_{\theta JA}$ ) is 22.2 °C/W for the DDW package.

Assuming 25°C ambient temperature, the junction temperature for the DDW package is calculated as shown below -

T<sub>J</sub> = 25°C + (3.66-W x 22.2 °C/W) = 106.3 °C

For more accurate calculation, consider the dependency of on-resistance of FETs with device junction temperature, as explained in  $\ddagger 8.1.1.2.2$  and  $\ddagger 8.1.2.3$ .

(19)

The DDV package with heat sink mounted on top will be able to deliver up to 10A current to both brushed-DC motors.

### 8.1.3.4 Driving Single Brushed-DC Motor

The outputs of DRV8962 can be connected in parallel to increase the drive current. 🛽 8-6 shows the schematic of DRV8962 driving a single brushed-DC motor.

图 8-6. Driving Single Brushed-DC motor with DRV8962

In this mode, a minimum of 30 nH to 100 nH inductance or a ferrite bead is required after the output pins before connecting the two channels together. This will help to prevent any shoot through between two paralleled channels during switching transient due to mismatch of paralleled channels (for example, asymmetric PCB layout, etc).

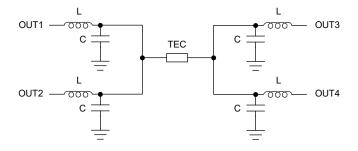

### 8.1.4 Driving Thermoelectric Coolers (TEC)

Thermoelectric coolers (TEC) work according to the Peltier effect. When a voltage is applied across the TEC, a DC current flows through the junction of the semiconductors, causing a temperature difference. Heat is transferred from one side of the TEC to the other. This creates a "hot" and a "cold" side of the TEC element. If the DC current is reversed, the hot and cold sides reverse as well.

A common way of modulating the current through the TEC is to use PWM driving and make the average current change by varying the ON and OFF duty cycles. To allow both heating and cooling from a single supply, a H-bridge topology is required. The DRV8962 can drive two H-bridges to drive two TECs bi-directionally with up to 5-A current. Pair of half-bridges can also be paralleled together to drive a single TEC with up to 10-A current.

The DRV8962 also features integrated current sensing and current sense output (IPROPI) with  $\pm$  4% accuracy to eliminate the need for two external shunt resistors in a closed-loop control topology, saving bill-of-materials cost and space. 🛛 8-7 shows the schematic of two TECs connected to a DRV8962 driver.

图 8-7. Driving two TECs

图 8-8 shows the schematic to drive one TEC with higher current.

图 8-8. Driving one TEC with higher current

The LC filters connected to the output nodes convert the PWM output from the DRV8962 into a low-ripple DC voltage across the TEC. The filters are required to minimize the ripple current, because fast transients (e.g., square wave power) can shorten the life of the TEC. The maximum ripple current is recommended to be less than 10% of maximum current. The maximum temperature differential across the TEC, which decreases as ripple current increases, is calculated with the following equation:

$$\Delta T = \Delta T_{MAX} / (1 + N^2)$$

(20)

Where  $\triangle T$  is actual temperature differential,  $\triangle T_{MAX}$  is maximum possible temperature differential specified in the TEC datasheet, N is the ratio between ripple and maximum current. N should not be greater than 0.1.

The choice of the input PWM frequency is a trade-off between switching loss and use of smaller inductors and capacitors. High PWM frequency also means that the voltage across the TEC can be tightly controlled, and the LC components can potentially be cheaper.

The transfer function of a second order low-pass filter is shown in :

H (j

$$\omega$$

) = 1 / (1 - ( $\omega$  /  $\omega_0$ )<sup>2</sup> + j $\omega$  / Q $\omega_0$ )

(21)

Where,

$\omega_0$  = 1 /  $\sqrt{(LC)}$ , resonant frequency of the filter

Q = quality factor

ω = DRV8962 input PWM frequency

The resonant frequency for the filter is typically chosen to be at least one order of magnitude lower than the PWM frequency. With this assumption, j程式 20 may be simplified to -

H in dB = -40 log ( $f_{\rm S}/f_{\rm 0}$ )

Where  $f_0$  = 1/ 2  $\pi \, \checkmark$  (LC) and  $f_S$  is the input PWM switching frequency.

- If L = 10  $\mu$  H and C = 22  $\mu$  F, the resonant frequency is 10.7 kHz.

- This resonant frequency corresponds to 39 dB of attenuation at 100 kHz switching frequency.

- For VM = 48 V, 39 dB attenuation means that the amount of ripple voltage across the TEC element will be approximately 550 mV.

- For a TEC element with a resistance of 1.5  $\Omega$ , the ripple current through the TEC will therefore be 366 mA.

- At the 5-A maximum output current of the DRV8962, 366 mA corresponds to 7.32% ripple current.

- This will cause about 0.5% reduction of the maximum temperature differential of the TEC element, as per 方 程式 20.

Adjust the LC values according to the supply voltage and DC current through the TEC element. The DRV8962 supports up to 200 kHz input PWM frequency. The power loss in the device at any given ambient temperature must be carefully considered before selecting the input PWM frequency.

Closing the loop on current is important in some TEC based heating and cooling systems. The DRV8962 can achieve this without the need for external current shunt resistors. Internal current mirrors are used to monitor the currents in each half-bridge and this information is available on IPROPI pins. A microcontroller can monitor and adjust the PWM duty based on the IPROPI pin voltage. When driving two TECs, connect the IPROPI pins of the corresponding half-bridges together to measure the H-bridge current. For example, for the schematic shown in 8-7, IPROPI1 and IPROPI2 are tied together, and IPROPI3 and IPROPI4 are also together. When driving only one TEC as shown in 8-8, tie all the IPROPI pins together.

Additionally, the DRV8962 can regulate the current internally by providing an external voltage reference (VREF) to the device to adjust the current regulation trip point. The current loop would then be closed within the H-bridge itself.

# 8.1.5 Driving Brushless DC Motors

The DRV8962 can also be used to drive a three-phase brushless DC (BLDC) motor. The DRV8962 supports independent control of three phases required to drive the BLDC motor. One of the four half-bridges of the DRV8962 can be disabled while driving a BLDC motor, by connecting the corresponding EN pin to ground. Shows a schematic of the DRV8962 driving a BLDC motor.

# 图 8-9. Driving BLDC Motor with DRV8962

The three half-bridges required to drive a BLDC motor can be controlled by six inputs - EN1, EN2, EN3 and IN1, IN2, IN3.

- When EN1 is low, OUT1 becomes high-impedance, allowing current to flow through the internal body diodes of the high-side and low-side FETs.

- When EN1 is high and IN1 is low, OUT1 is driven low with its low-side FET enabled.

- When EN1 is high and IN1 is high, OUT1 is driven high with its high-side FET enabled.

- Likewise is true for OUT2 and OUT3.

- EN4 can be grounded to permanently disable OUT4.

A minimum of 30 nH to 100 nH inductance or a ferrite bead has to be connected after the output pins. This will help to prevent any shoot through due to mismatch between channels (for example, process variation, unsymmetrical PCB layout, etc).

The IPROPI pins output a current proportional to the current flowing through the high-side FET of each halfbridge. The IPROPI output accuracy at maximum rated current is  $\pm 4\%$ .

### $I_{PROPI} = I_{HS} \times A_{IPROPI}$

Each IPROPI pin should be connected to an external resistor ( $R_{IPROPI}$ ) to ground in order to generate a proportional voltage ( $V_{IPROPI}$ ) on the IPROPI pin. This allows for the load current to be measured as the voltage drop across the  $R_{IPROPI}$  resistor with a standard analog to digital converter (ADC).

# V<sub>IPROPI</sub> = IPROPI x R<sub>IPROPI</sub>

If higher accuracy of current sensing is required, external sense resistors can be placed between the PGND pins and system ground. The voltage drop across the external sense resistor should not exceed 300 mV.

**ADVANCE INFORMATION**

# 9 Package Thermal Considerations

# 9.1 DDW Package

Thermal pad of the DDW package is attached at bottom of device to improve the thermal capability of the device. The thermal pad has to be soldered with a very good coverage on PCB to deliver the power specified in the data sheet. Refer to the  $\ddagger$  11.1 section for more details.

### 9.2 DDV Package