- ÖĘŌģ³§ÉĢ£ŗTI

- ²śĘ·Ąą±š£ŗĪ¢æŲÖĘĘ÷ (MCU) ŗĶ“¦ĄķĘ÷

- ¼¼ŹõĄąÄæ£ŗ“¦ĄķĘ÷ - Źż×ÖŠÅŗÅ“¦ĄķĘ÷ (DSP)

- ¹¦ÄÜĆčŹö£ŗC64x ¶Øµć DSP - 500MHz”¢McBSP”¢McASP”¢I2cC

- µć»÷ÕāĄļ“ņæŖ¼°ĻĀŌŲTMS320C6413µÄ¼¼ŹõĪĵµ×ŹĮĻ

- TI“śĄķĒžµĄ£¬Ģį¹©µ±ČÕ·¢»õ”¢ŃĻøńµÄÖŹĮæ±ź×¼£¬Āś×ćÄśµÄÄæ±ź¼Ūøń

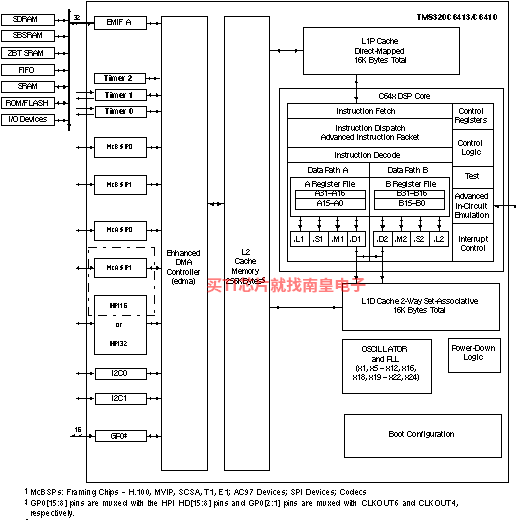

The TMS320C64x™ DSPs (including the TMS320C6413, TMS320C6410 devices) are the highest-performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The TMS320C6413 and TMS320C6410 (C6413 and C6410) devices are based on the second-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture (VelociTI.2™) developed by Texas Instruments (TI)™ The high-performance, lower-cost C6413/C6410 DSPs enable customers to reduce system costs for telecom, medical, industrial, office, and photo lab equipment. The C64x™ is a code-compatible member of the C6000™ DSP platform.

With performance of up to 4000 million instructions per second (MIPS) at a clock rate of 500 MHz, the C6413 device offers cost-effective solutions to high-performance DSP programming challenges.

With performance of up to 3200 million instructions per second (MIPS) at a clock rate of 400 MHz, the C6410 device offers cost-effective solutions to high-performance DSP programming challenges. The C6410 device also provides excellent value for packet telephony and for other cost-sensitive applications demanding high performance. The C6410 device also provides excellent value for packet telephony and to other cost-sensitive applications demanding high performance

The C6413/C6410 DSP possesses the operational flexibility of high-speed controllers and the numerical capability of array processors. The C64x™ DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly independent functional units—two multipliers for a 32-bit result and six arithmetic logic units (ALUs)— with VelociTI.2™ extensions. The VelociTI.2™ extensions in the eight functional units include new instructions to accelerate the performance in video and imaging applications and extend the parallelism of the VelociTI™ architecture. The C6413 can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 2000 million MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 4000 MMACS. The C6410 can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 1600 million MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 3200 MMACS. The C6413/C6410 DSP also has application-specific hardware logic, on-chip memory, and additional on-chip peripherals similar to the other C6000™ DSP platform devices.

The C6413/C6410 uses a two-level cache-based architecture and has a powerful and diverse set of peripherals. The Level 1 program cache (L1P) is a 128-Kbit direct mapped cache and the Level 1 data cache (L1D) is a 128-Kbit 2-way set-associative cache. The Level 2 memory/cache (L2) consists of an 2-Mbit memory space that is shared between program and data space [for C6413 device] and the Level 2 memory/cache (L2) consists of an 1-Mbit memory space that is shared between program and data space [for C6410 device]. L2 memory can be configured as mapped memory, cache, or combinations of the two. The peripheral set includes: two multichannel buffered audio serial ports (McASPs); two inter-integrated circuit bus modules (I2Cs) ; two multichannel buffered serial ports (McBSPs); three 32-bit general-purpose timers; a user-configurable 16-bit or 32-bit host-port interface (HPI16/HPI32); a 16-pin general-purpose input/output port (GP0) with programmable interrupt/event generation modes; and a 32-bit glueless external memory interface (EMIFA), which is capable of interfacing to synchronous and asynchronous memories and peripherals.

The McASP port supports one transmit and one receive clock zone, with eight serial data pins which can be individually allocated to any of the two zones. The serial port supports time-division multiplexing on each pin from 2 to 32 time slots. The C6413/C6410 has sufficient bandwidth to support all 8 serial data pins transmitting a 192-kHz stereo signal. Serial data in each zone may be transmitted and received on multiple serial data pins simultaneously and formatted in a multitude of variations on the Philips Inter-IC Sound (I2S) format.

In addition, the McASP transmitter may be programmed to output multiple S/PDIF, IEC60958, AES-3, CP-430 encoded data channels simultaneously, with a single RAM containing the full implementation of user data and channel status fields.

McASP also provides extensive error-checking and recovery features, such as the bad clock detection circuit for each high-frequency master clock which verifies that the master clock is within a programmed frequency range.

The I2C ports on the TMS320C6413/C6410 allows the DSP to easily control peripheral devices and communicate with a host processor. In addition, the standard multichannel buffered serial port (McBSP) may be used to communicate with serial peripheral interface (SPI) mode peripheral devices.

TheC6413/C6410 has a complete set of development tools which includes: a new C compiler, an assembly optimizer to simplify programming and scheduling, and a Windows™ debugger interface for visibility into source code execution.

- High-Performance Fixed-Point Digital Signal Processor (TMS320C6413/C6410)

- TMS320C6413

- 2-ns Instruction Cycle Time

- 500-MHz Clock Rate

- 4000 MIPS

- TMS320C6410

- 2.5-ns Instruction Cycle Time

- 400-MHz Clock Rate

- 3200 MIPS

- Eight 32-Bit Instructions/Cycle

- Fully Software-Compatible With C64x

- Extended Temperature Devices Available

- TMS320C6413

- VelociTI.2 Extensions to VelociTI Advanced Very-Long-Instruction-Word (VLIW) TMS320C64x DSP Core

- Eight Highly Independent Functional Units With VelociTI.2 Extensions:

- Six ALUs (32-/40-Bit), Each Supports Single 32-Bit, Dual 16-Bit, or Quad 8-Bit Arithmetic per Clock Cycle

- Two Multipliers Support Four 16 x 16-Bit Multiplies (32-Bit Results) per Clock Cycle or Eight 8 x 8-Bit Multiplies (16-Bit Results) per Clock Cycle

- Load-Store Architecture With Non-Aligned Support

- 64 32-Bit General-Purpose Registers

- Instruction Packing Reduces Code Size

- All Instructions Conditional

- Eight Highly Independent Functional Units With VelociTI.2 Extensions:

- Instruction Set Features

- Byte-Addressable (8-/16-/32-/64-Bit Data)

- 8-Bit Overflow Protection

- Bit-Field Extract, Set, Clear

- Normalization, Saturation, Bit-Counting

- VelociTI.2 Increased Orthogonality

- VelociTI.2 Extensions to VelociTI Advanced Very-Long-Instruction-Word (VLIW) TMS320C64x DSP Core

- L1/L2 Memory Architecture

- 128K-Bit (16K-Byte) L1P Program Cache (Direct Mapped)

- 128K-Bit (16K-Byte) L1D Data Cache (2-Way Set-Associative)

- 2M-Bit (256K-Byte) L2 Unified Mapped RAM/Cache [C6413] (Flexible RAM/Cache Allocation)

- 1M-Bit (128K-Byte) L2 Unified Mapped RAM/Cache [C6410] (Flexible RAM/Cache Allocation)

- Endianess: Little Endian, Big Endian

- 32-Bit External Memory Interface (EMIF)

- Glueless Interface to Asynchronous Memories (SRAM and EPROM) and Synchronous Memories (SDRAM, SBSRAM, ZBT SRAM, and FIFO)

- 512M-Byte Total Addressable External Memory Space

- Enhanced Direct-Memory-Access (EDMA) Controller (64 Independent Channels)

- Host-Port Interface (HPI) [32-/16-Bit]

- Two Multichannel Audio Serial Ports (McASPs) - with Six Serial Data Pins each

- Two Inter-Integrated Circuit (I2C) Buses

- Additional GPIO Capability

- Two Multichannel Buffered Serial Ports

- Three 32-Bit General-Purpose Timers

- Sixteen General-Purpose I/O (GPIO) Pins

- Flexible PLL Clock Generator

- On-Chip Fundamental Oscillator

- IEEE-1149.1 (JTAG) Boundary-Scan-Compatible

- 288-Pin Ball Grid Array (BGA) Package (GTS and ZTS Suffixes), 1.0-mm Ball Pitch

- 0.13-m/6-Level Cu Metal Process (CMOS)

- 3.3-V I/Os, 1.2-V Internal

VelociTI.2, VelociTI, and TMS320C64x are trademarks of Texas Instruments. All trademarks are the property of their respective owners. IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture. TMS320C6000, and C6000 are trademarks of Texas Instruments.

- DSP

- 1 C64x

- DSP MHz (Max)

- 500

- CPU

- 32-/64-bit

- Operating system

- DSP/BIOS

- Rating

- Catalog

- Operating temperature range (C)

- -40 to 105, 0 to 90

TMS320C6413µÄĶźÕūŠĶŗÅÓŠ£ŗTMS320C6413GTS500”¢TMS320C6413GTSA500”¢TMS320C6413ZTS500”¢TMS320C6413ZTSA500£¬ŅŌĻĀŹĒÕāŠ©²śĘ·µÄ¹Ų¼ü²ĪŹż¼°¹ŁĶų²É¹ŗ±Ø¼Ū£ŗ

TMS320C6413GTS500£¬¹¤×÷ĪĀ¶Č£ŗ0 to 90£¬·ā×°£ŗFCBGA (GTS)-288£¬°ü×°ŹżĮæMPQ£ŗ60øö£¬MSL µČ¼¶/»ŲĮ÷ŗø·åÖµĪĀ¶Č£ŗLevel-4-220C-72 HR£¬Ņż½Å¶Ę²ć/ŗøĒņ²ÄĮĻ£ŗSNPB£¬TI¹ŁĶųTMS320C6413GTS500µÄÅśĮæUSD¼Ūøń£ŗ22.739£Ø1000+£©

TMS320C6413GTSA500£¬¹¤×÷ĪĀ¶Č£ŗ-40 to 105£¬·ā×°£ŗFCBGA (GTS)-288£¬°ü×°ŹżĮæMPQ£ŗ60øö£¬MSL µČ¼¶/»ŲĮ÷ŗø·åÖµĪĀ¶Č£ŗLevel-4-220C-72 HR£¬Ņż½Å¶Ę²ć/ŗøĒņ²ÄĮĻ£ŗSNPB£¬TI¹ŁĶųTMS320C6413GTSA500µÄÅśĮæUSD¼Ūøń£ŗ27.287£Ø1000+£©

TMS320C6413ZTS500£¬¹¤×÷ĪĀ¶Č£ŗ0 to 90£¬·ā×°£ŗFCBGA (ZTS)-288£¬°ü×°ŹżĮæMPQ£ŗ60øö£¬MSL µČ¼¶/»ŲĮ÷ŗø·åÖµĪĀ¶Č£ŗLevel-4-260C-72HR£¬Ņż½Å¶Ę²ć/ŗøĒņ²ÄĮĻ£ŗSNAGCU£¬TI¹ŁĶųTMS320C6413ZTS500µÄÅśĮæUSD¼Ūøń£ŗ22.739£Ø1000+£©

TMS320C6413ZTSA500£¬¹¤×÷ĪĀ¶Č£ŗ-40 to 105£¬·ā×°£ŗFCBGA (ZTS)-288£¬°ü×°ŹżĮæMPQ£ŗ60øö£¬MSL µČ¼¶/»ŲĮ÷ŗø·åÖµĪĀ¶Č£ŗLevel-4-260C-72HR£¬Ņż½Å¶Ę²ć/ŗøĒņ²ÄĮĻ£ŗSNAGCU£¬TI¹ŁĶųTMS320C6413ZTSA500µÄÅśĮæUSD¼Ūøń£ŗ27.287£Ø1000+£©

TMDSEMU560V2STM-U Blackhawk XDS560v2 ĻµĶ³øś×Ł USB ·ĀÕęĘ÷

XDS560v2 System Trace ŹĒ XDS560v2 ĻµĮŠøߊŌÄÜ TI “¦ĄķĘ÷µ÷ŹŌĢ½Õė£Ø·ĀÕęĘ÷£©µÄµŚŅ»ÖÖŠĶŗÅ”£XDS560v2 ŹĒ XDS ĻµĮŠµ÷ŹŌĢ½ÕėÖŠŠŌÄÜ×īøßµÄŅ»æī£¬Ķ¬Ź±Ö§³Ö“«Ķ³ JTAG ±ź×¼ (IEEE1149.1) ŗĶ cJTAG (IEEE1149.7)”£

XDS560v2 System Trace ŌŚĘ侎“óµÄĶā²æ“ę“¢Ę÷»ŗ³åĒųÖŠ¼ÓČėĮĖĻµĶ³Ņż½Åøś×Ł”£ÕāÖÖĶā²æ“ę“¢Ę÷»ŗ³åĒųŹŹÓĆÓŚÖø¶ØµÄ TI Ę÷¼ž£¬Ķعż²¶»ńĻą¹ŲĘ÷¼ž¼¶ŠÅĻ¢£¬»ńµĆ×¼Č·µÄ×ÜĻߊŌÄÜ»ī¶ÆŗĶĶĢĶĀĮ棬²¢¶ŌÄŚŗĖŗĶĶāÉč½ųŠŠµēŌ“¹ÜĄķ”£“ĖĶā£¬¶ŌÓŚ“ųÓŠĒ¶ČėŹ½»ŗ³åøś×ŁĘ÷ (ETB) µÄĖłÓŠ ARM ŗĶ DSP “¦ĄķĘ÷£¬ĖłÓŠ XDS (...)

TMDSEMU560V2STM-UE Spectrum Digital XDS560v2 ĻµĶ³øś×Ł USB ŗĶŅŌĢ«Ķų

XDS560v2 System Trace ŹĒ XDS560v2 ĻµĮŠøߊŌÄÜ TI “¦ĄķĘ÷µ÷ŹŌĢ½Õė£Ø·ĀÕęĘ÷£©µÄµŚŅ»ÖÖŠĶŗÅ”£XDS560v2 ŹĒ XDS ĻµĮŠµ÷ŹŌĢ½ÕėÖŠŠŌÄÜ×īøßµÄŅ»æī£¬Ķ¬Ź±Ö§³Ö“«Ķ³ JTAG ±ź×¼ (IEEE1149.1) ŗĶ cJTAG (IEEE1149.7)”£

XDS560v2 System Trace ŌŚĘ侎“óµÄĶā²æ“ę“¢Ę÷»ŗ³åĒųÖŠ¼ÓČėĮĖĻµĶ³Ņż½Åøś×Ł”£ÕāÖÖĶā²æ“ę“¢Ę÷»ŗ³åĒųŹŹÓĆÓŚÖø¶ØµÄ TI Ę÷¼ž£¬Ķعż²¶»ńĻą¹ŲĘ÷¼ž¼¶ŠÅĻ¢£¬»ńµĆ×¼Č·µÄ×ÜĻߊŌÄÜ»ī¶ÆŗĶĶĢĶĀĮ棬²¢¶ŌÄŚŗĖŗĶĶāÉč½ųŠŠµēŌ“¹ÜĄķ”£“ĖĶā£¬¶ŌÓŚ“ųÓŠĒ¶ČėŹ½»ŗ³åøś×ŁĘ÷ (ETB) µÄĖłÓŠ ARM ŗĶ DSP “¦ĄķĘ÷£¬ĖłÓŠ XDS (...)

CCSTUDIO — Code Composer Studio ¼Æ³ÉŹ½æŖ·¢»·¾³ (IDE)

C5000/6000 Image Processing Library (IMGLIB) is an optimized image/video processing function library for C programmers. It includes C-callable general-purpose image/video processing routines that are typically used in computationally intensive real-time applications. With these routines, higher (...)SPRC265 TMS320C6000 DSP æā (DSPLIB)

TMS320C6000 Digital Signal Processor Library (DSPLIB) is a platform-optimized DSP function library for C programmers. It includes C-callable, general-purpose signal-processing routines that are typically used in computationally intensive real-time applications. With these routines, higher (...)TELECOMLIB ÓĆÓŚ TMS320C64x+ ŗĶ TMS320C55x “¦ĄķĘ÷µÄµēŠÅŗĶĆ½Ģåæā - FAXLIB”¢VoLIB ŗĶ AEC/AER

Voice Library- VoLIBprovides components that, together, facilitate the development of the signal processing chain for Voice over IP applications such as infrastructure, enterprise, residential gateways and IP phones. Together with optimized implementations of ITU-T voice codecs, that can be (...)C6413 GTS BSDL Model (Rev. B)

TI has partnered with companies to offer a wide range of software, tools, and SOMs using TI processors to accelerate your path to production. Download this search tool to quickly browse our third-party solutions and find the right third-party to meet your needs. The software, tools and modules (...)